Multi-Level Buffer Management and Storage System Design for Non-Volatile Memory

📝 Original Paper Info

- Title: Multi-Tier Buffer Management and Storage System Design for Non-Volatile Memory- ArXiv ID: 1901.10938

- Date: 2019-01-31

- Authors: Joy Arulraj, Andy Pavlo, Krishna Teja Malladi

📝 Abstract

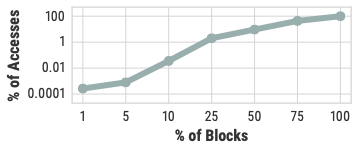

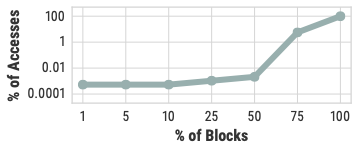

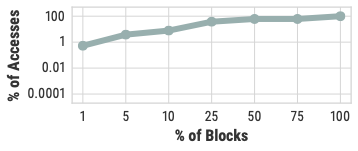

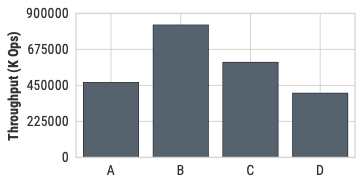

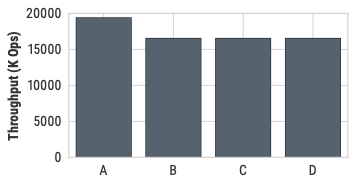

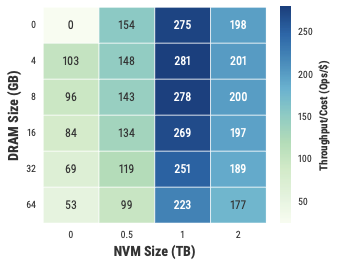

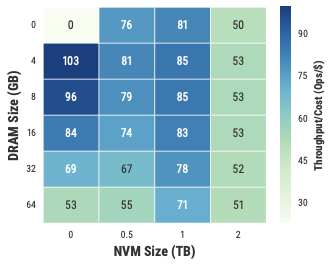

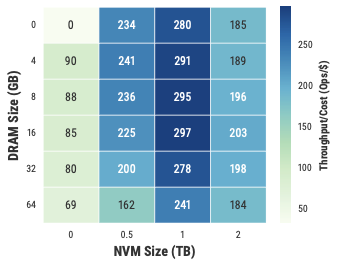

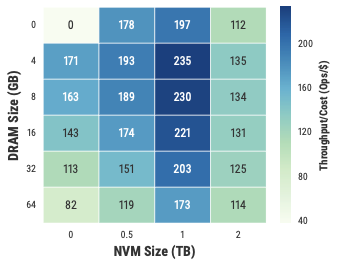

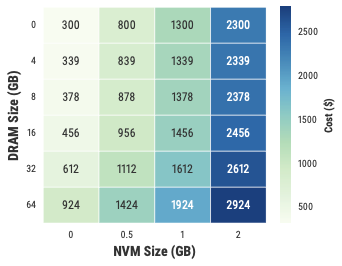

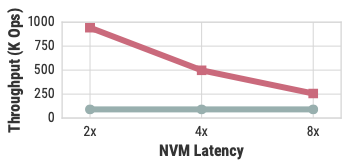

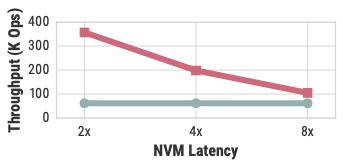

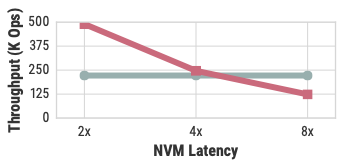

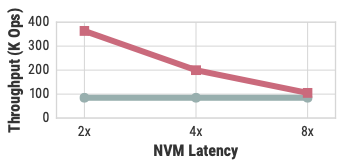

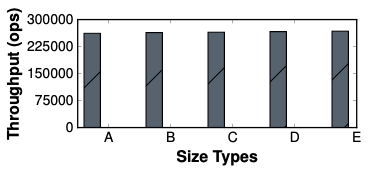

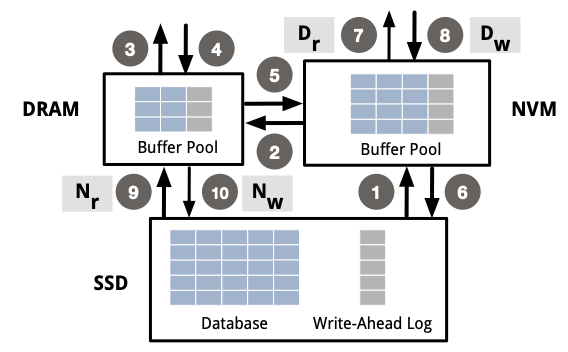

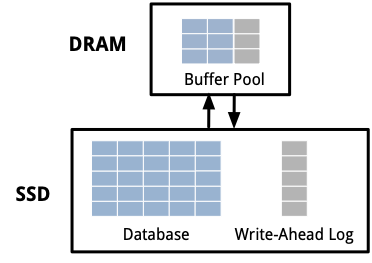

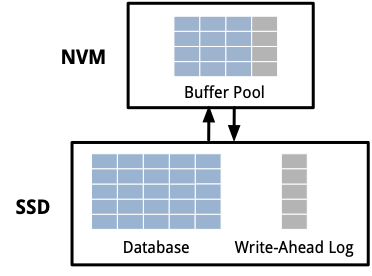

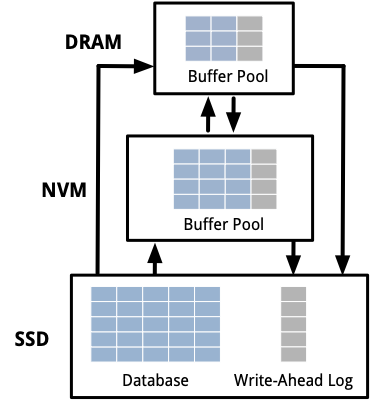

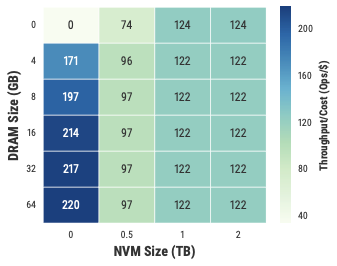

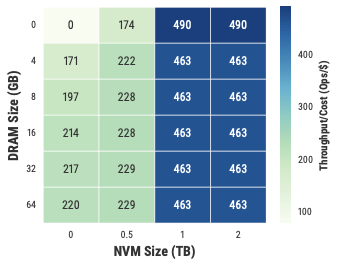

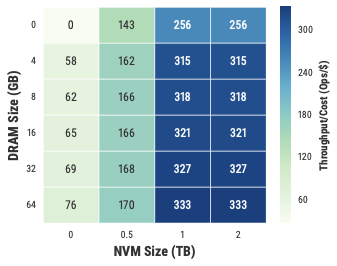

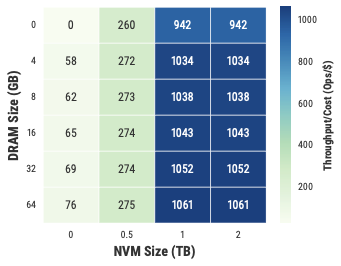

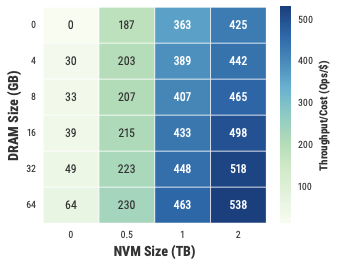

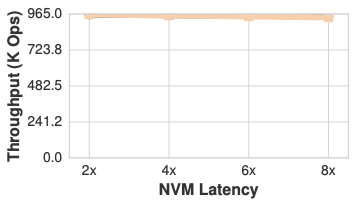

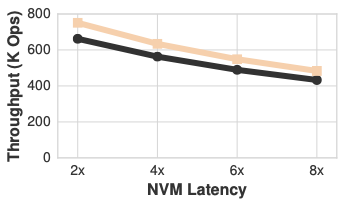

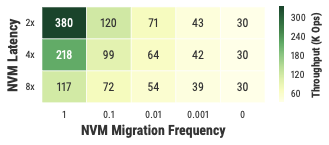

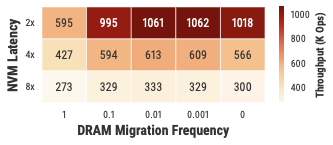

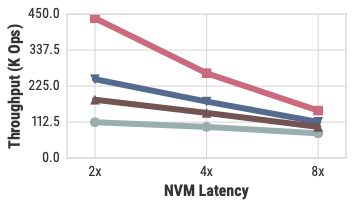

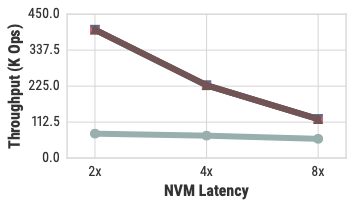

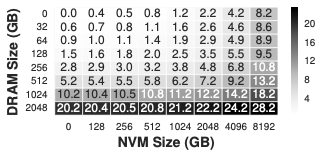

The design of the buffer manager in database management systems (DBMSs) is influenced by the performance characteristics of volatile memory (DRAM) and non-volatile storage (e.g., SSD). The key design assumptions have been that the data must be migrated to DRAM for the DBMS to operate on it and that storage is orders of magnitude slower than DRAM. But the arrival of new non-volatile memory (NVM) technologies that are nearly as fast as DRAM invalidates these previous assumptions. This paper presents techniques for managing and designing a multi-tier storage hierarchy comprising of DRAM, NVM, and SSD. Our main technical contributions are a multi-tier buffer manager and a storage system designer that leverage the characteristics of NVM. We propose a set of optimizations for maximizing the utility of data migration between different devices in the storage hierarchy. We demonstrate that these optimizations have to be tailored based on device and workload characteristics. Given this, we present a technique for adapting these optimizations to achieve a near-optimal buffer management policy for an arbitrary workload and storage hierarchy without requiring any manual tuning. We finally present a recommendation system for designing a multi-tier storage hierarchy for a target workload and system cost budget. Our results show that the NVM-aware buffer manager and storage system designer improve throughput and reduce system cost across different transaction and analytical processing workloads.💡 Summary & Analysis

This paper delves into the impact of new non-volatile memory (NVM) technologies on database management system (DBMS) buffer manager design, particularly focusing on optimizing NVM use in a multi-tier storage hierarchy that includes DRAM and SSD. The traditional assumption has been that data must be moved to DRAM for processing, with storage being significantly slower than DRAM. However, the advent of NVM technologies, which are nearly as fast as DRAM, challenges these assumptions.To address this issue, the authors propose a new multi-tier buffer manager designed specifically for systems using DRAM, NVM, and SSD. This system includes several optimizations aimed at maximizing the efficiency of data migration between different storage devices within the hierarchy. The key innovation lies in adapting these optimizations automatically based on both device characteristics and workload requirements without manual tuning.

The research demonstrates that this approach significantly improves performance across various transactional and analytical processing workloads while also reducing overall system costs. This is crucial as NVM technologies become more prevalent, offering a pathway for future data centers to operate faster and more efficiently.

📄 Full Paper Content (ArXiv Source)

📊 논문 시각자료 (Figures)