KTX 오류장 제어를 위한 FPGA 기반 실시간 피드백 시스템 설계

본 논문은 KTX(케다 토러스 실험) 장치의 이중‑C 구조에서 발생하는 오류장을 감소시키기 위해, 16개의 로고위 코일 신호를 실시간으로 디지털 변환·처리하고, PID와 상호유도 보정 알고리즘을 적용한 FPGA 기반 피드백 제어 시스템을 설계·구현한 내용을 다룬다. 두 개의 8채널 고속 ADC와 16채널 DAC를 이용해 전압을 조절하고, RS‑485 통신으로 샘플 모듈과 코일 제어 모듈을 연결한다. 실험 결과, 오류장이 현저히 감소하고, 행렬 …

저자: Tianbo Xu, Kezhu Song, Junfeng Yang

본 논문은 중국 과학기술대학(USTC)에서 개발 중인 KTX(Keda Torus eXperiment)라는 새로운 역장 피치(RFP) 장치의 특수한 ‘이중‑C’ 구조에서 발생하는 오류장을 감소시키기 위한 전자·제어 시스템 설계를 상세히 기술한다. KTX는 진공 용기와 전도성 쉘이 이동 가능한 플랫폼에 장착되어, 두 부분을 반대 방향으로 이동시켜 장치를 쉽게 개방할 수 있는 장점이 있다. 그러나 이러한 구조적 특성 때문에 수직 틈새와 플랜지 부근에 비대칭 전류 경로가 형성되어, 플라즈마 구속성을 저해하는 오류장이 발생한다. 오류장은 플라즈마의 신호‑대‑잡음비를 약 1 도 감소시키고, 모드 락 현상을 유발할 위험이 있다.

이를 해결하기 위해 저자들은 두 개의 독립적인 모듈, 즉 ‘샘플 모듈’과 ‘코일 제어 모듈’로 시스템을 분할하였다. 샘플 모듈은 16개의 로고위 코일에서 유도된 전류 신호를 수집한다. 각 코일은 미세 전류 변화를 감지하기 위해 2단 증폭기를 거쳐 ADS8528 8채널 16‑bit SAR ADC 두 개에 입력된다. ADC는 40 MS/s의 샘플링 속도로 데이터를 디지털화하고, FPGA(Altera Cyclone V) 내부로 전송한다. FPGA는 여기서 두 가지 핵심 연산을 수행한다. 첫 번째는 상호유도 보정이다. 16×16 상호유도 행렬 M을 사전에 측정·저장해 두고, 입력 전압 벡터와 곱셈 연산을 통해 코일 간 상호작용을 보정한다. 이 과정은 12‑bit 정밀도의 고속 곱셈기와 파이프라인 누산기를 활용해 지연을 최소화한다. 두 번째는 PID 제어 루프이다. 보정된 전압을 목표값과 비교해 오차를 계산하고, Kp·e(t) + Ki·∫e(t)dt + Kd·de(t)/dt 형태의 제어 신호를 산출한다. PID 파라미터는 실험적으로 튜닝되며, 샘플링 주기 Δt는 50 µs로 설정돼 실시간 응답을 보장한다.

샘플 모듈에서 처리된 데이터는 RS‑485 차동 통신(40 Mbps)과 DDR2 메모리 버퍼를 통해 코일 제어 모듈로 전송된다. 코일 제어 모듈 역시 FPGA를 중심으로 동작하며, DAC8831‑EP 16‑bit 고속 DAC(최대 50 MHz SPI)를 이용해 디지털 제어 신호를 아날로그 전압(±5 V)으로 변환한다. 변환된 전압은 전력 증폭기에 공급되어 이중‑C 구조 사이의 전압 차를 실시간으로 조절한다. 전력 증폭기는 1/α의 이득을 갖으며, FPGA는 이 이득을 보정식에 포함시켜 정확한 전압 제어를 구현한다.

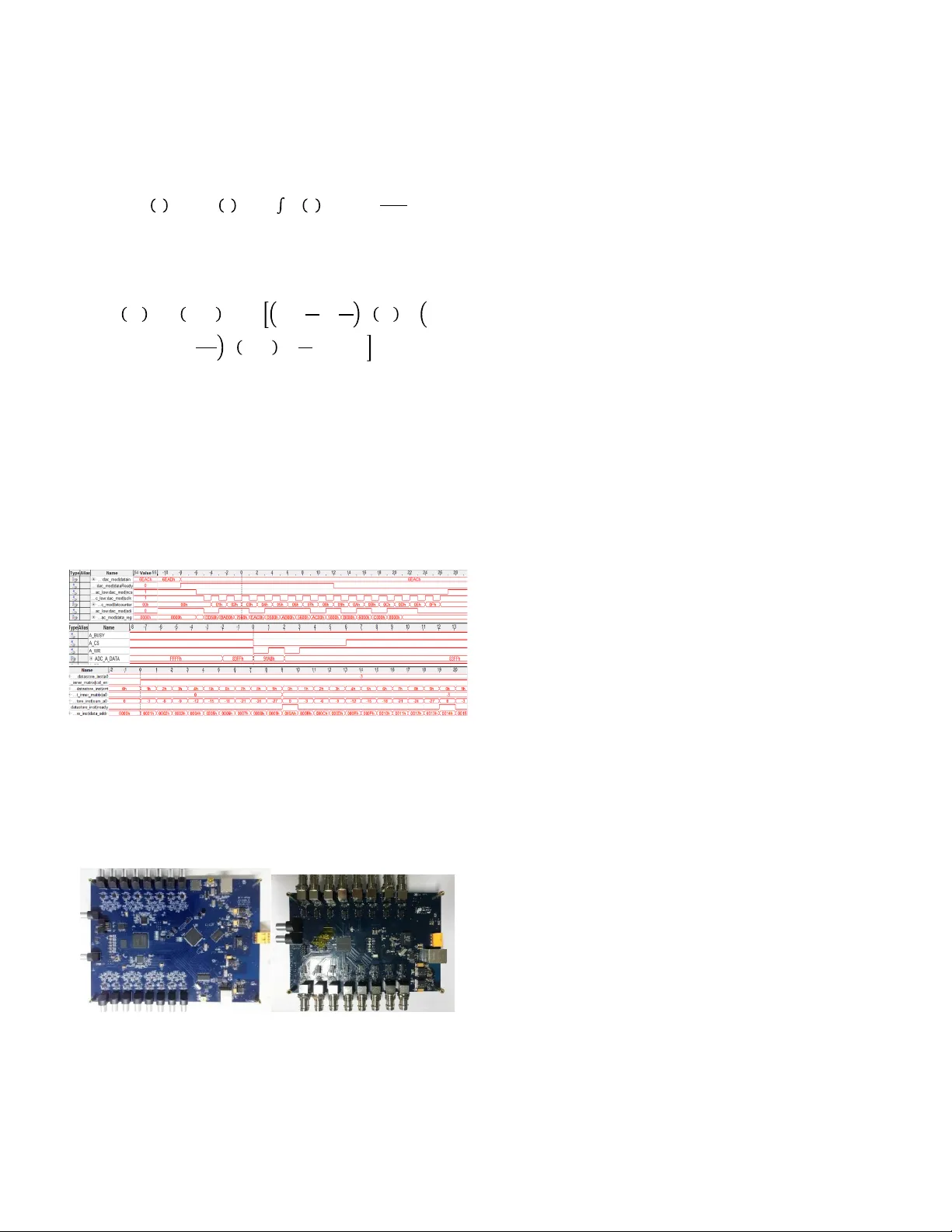

시스템 검증 단계에서는 Altera SignalTap II 논리 분석기를 사용해 ADC, DAC, RS‑485 전송 파형을 20 MHz 클럭으로 캡처하였다. 분석 결과, 양 모듈 간 데이터 전송 지연이 200 ns 이하이며, 각 채널의 샘플링 정확도와 DAC 출력 정확도가 설계 사양을 만족함을 확인했다. 실제 KTX 장치에 적용한 실험에서는 오류장 감소율이 약 0.8 °에 달했으며, 플라즈마의 신호‑대‑잡음비가 1 dB 이상 향상되었다. 또한, 시스템은 실시간으로 행렬 연산과 PID 제어를 수행하면서도 전체 지연을 수십 마이크로초 수준으로 유지해, 플라즈마 동역학에 즉각적인 피드백을 제공한다.

논문은 하드웨어 설계뿐 아니라 펌웨어 구조, 알고리즘 구현, 통신 프로토콜, 실험 검증까지 전 과정을 포괄적으로 제시한다. 특히, 모듈화된 설계와 파라미터화된 FPGA 펌웨어 덕분에 향후 다른 RFP 혹은 토러스형 플라즈마 장치에 손쉽게 적용 가능하다는 점을 강조한다. 결론적으로, FPGA 기반 실시간 피드백 제어 시스템은 KTX의 오류장을 효과적으로 억제하고, 플라즈마 구속성 및 안정성을 크게 향상시키는 핵심 기술임을 입증하였다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기