FPGA 가속을 활용한 ADC 성능 보정 시스템

본 논문은 고속·고해상도 ADC의 성능 보정을 위해 PCIe 기반 DMA와 부동소수점 연산을 적용한 FPGA 가속 구조를 제안한다. FPGA가 PC 메모리에서 ADC 데이터 스트림을 직접 읽어 FFT 기반 스펙트럼 분석을 수행하고, 결과를 다시 PC 메모리로 반환한다. 실험 결과, CPU‑Only C++ 구현 대비 처리 시간이 2.19 ms에서 18 µs로 100배 이상 단축되었으며, 데이터 전송률은 440 MB/s에 달한다. 향후 대규모 AD…

저자: Guangyuan Yuan, Zhe cao, Shuwen Wang

본 논문은 고속·고해상도 아날로그‑디지털 변환기(ADC)가 물리 실험, 특히 고정밀 시·전하 측정에 널리 사용되는 현황을 출발점으로 한다. ADC가 생성하는 방대한 디지털 데이터는 기존 CPU 기반 소프트웨어 처리로는 실시간 분석에 한계가 있다. 이를 해결하고자 저자는 FPGA(Field‑Programmable Gate Array) 가속 구조를 설계하고, PCIe(Peripheral Component Interconnect Express) 기반 DMA(Direct Memory Access)를 통해 데이터 전송 효율을 극대화한다.

Ⅰ. 서론에서는 ADC의 핵심 동적 파라미터(SNR, SINAD, ENOB, THD, SFDR 등)의 중요성을 강조하고, FPGA가 제공하는 병렬·스트림 처리 특성이 이러한 파라미터 계산에 적합함을 언급한다. 또한 기존 연구(양자화, 고속 FFT 가속 등)를 인용해 본 연구의 차별점을 제시한다.

Ⅱ. 원리 및 방법에서는 ADC 성능 보정에 필요한 스펙트럼 분석이 FFT(Fast Fourier Transform)를 기반으로 수행된다는 점을 설명한다. N‑point FFT는 N·log₂N 복소수 곱셈을 필요로 하는데, FPGA 내부에서는 각 스테이지를 파이프라인화하고 동시에 여러 데이터 그룹을 처리함으로써 연산 지연을 최소화한다. 구체적으로 1024‑point FFT는 4258 클럭이 소요되며, FPGA 클럭을 250 MHz로 설정하면 전체 연산 시간은 약 17 µs가 된다.

데이터 흐름은 다음과 같다. PC 메모리에 저장된 ADC 샘플(64‑bit, 1024점) → PCIe DMA를 통해 FPGA 로드 → FPGA 내부 버퍼에 저장 → 부동소수점 FFT 연산 수행 → 스펙트럼 결과를 다시 PCIe DMA로 PC 메모리로 전송 → CPU가 최종 파라미터(SNR, ENOB 등) 계산. 이 과정에서 부동소수점 연산을 채택해 수치 정확도를 유지한다.

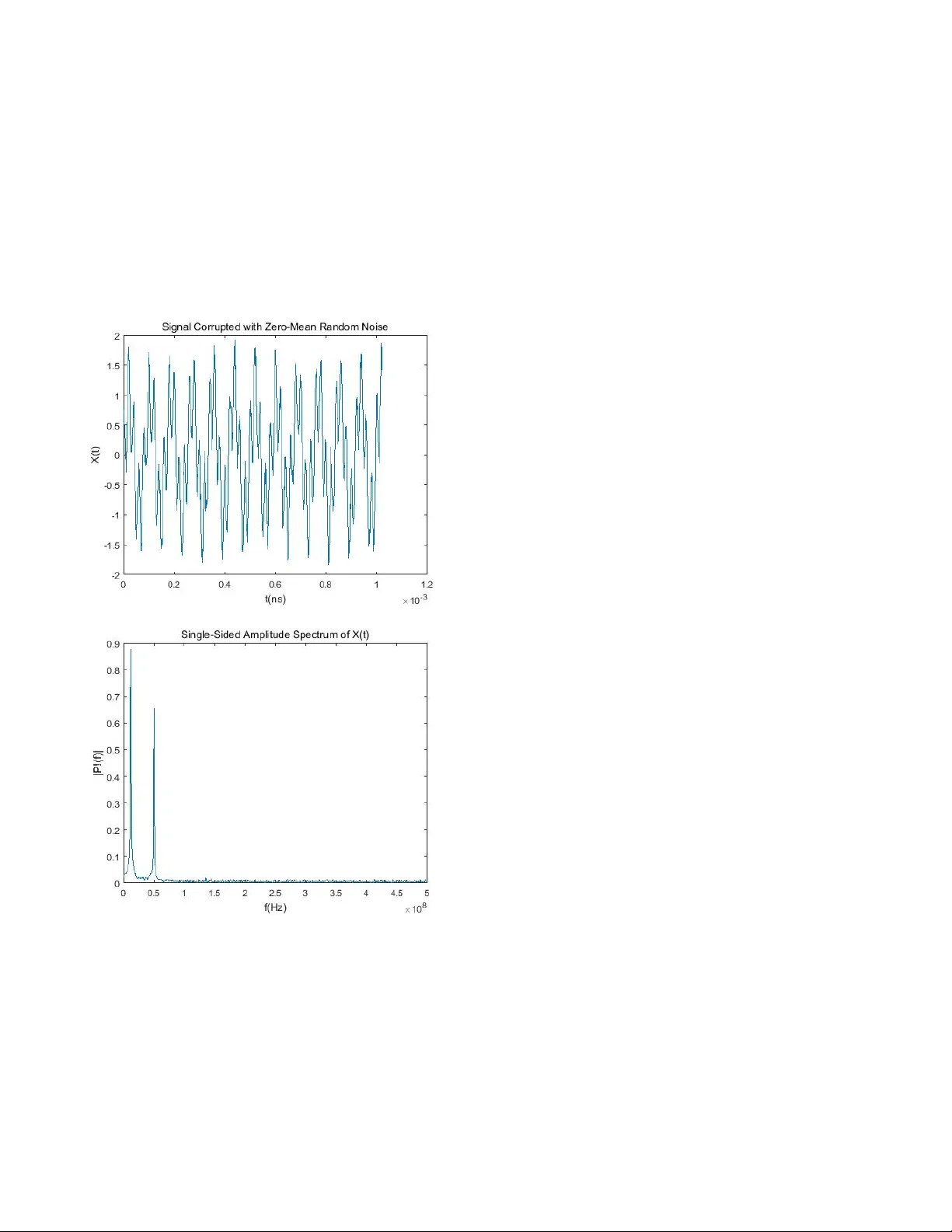

Ⅲ. 검증 테스트에서는 Xilinx Virtex‑7 XC7VX690T FPGA와 Intel Xeon E5‑2609 v4 CPU를 사용하였다. 테스트 데이터는 50 MHz와 12 MHz 사인파에 랜덤 노이즈를 합성한 신호이며, 1024‑point 64‑bit 실수 형태로 생성하였다. FPGA 가속 프로그램과 순수 CPU(C++) 프로그램을 각각 10⁹ 회 반복 실행해 평균 처리 시간을 측정했다. 결과는 CPU‑Only이 2.19 ms, FPGA 가속이 18 µs로 100배 이상 차이가 났으며, 전송률은 440 MB/s에 달했다. 또한 주파수 영역 결과는 두 구현 모두 동일하게 나타나 부동소수점 연산의 정확성을 확인했다.

Ⅳ. 논의에서는 연속 데이터 스트림을 제공할 경우 평균 처리 시간이 FFT 버스 한계인 2 GB/s(250 MHz 클럭 기준)까지 도달할 수 있음을 언급한다. 또한 추가 FFT 모듈을 FPGA에 배치하면 PCIe 버스 한계까지 성능을 끌어올릴 수 있다고 제안한다. ENOB, SNR, SINAD 등 다른 보정 파라미터도 FPGA 내에서 실시간 계산이 가능하므로, 온보드 보정 시스템으로 확장할 여지가 크다. 다만, 부동소수점 연산이 로직 자원을 많이 차지하고, 다채널(수천 개 ADC) 동시 처리 시 PCIe 대역폭이 병목이 될 수 있다는 제한점도 제시한다.

Ⅴ. 결론에서는 FPGA 기반 가속 구조가 ADC 성능 보정에 있어 처리 속도를 100배 이상 향상시키면서도 정확도는 CPU 구현과 동일함을 재확인한다. PCIe와 부동소수점 알고리즘을 결합한 설계는 대규모 ADC 배열(예: CCD 카메라) 실시간 보정에 적용 가능하며, 향후 멀티‑FFT 파이프라인 및 고대역폭 PCIe(Gen3/Gen4) 적용을 통해 더욱 높은 처리량을 달성할 수 있음을 강조한다.

참고문헌은 ADC 전반에 대한 서베이, FPGA 가속 사례, FFT 이론 등을 포함한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기