Application of FPGA Acceleration in ADC Performance Calibration

In recent years, high speed and high resolution analog-to-digital converter (ADC) is widely employed in many physical experiments, especially in high precision time and charge measurement. The rapid increasing amount of digitized data demands faster …

Authors: Guangyuan Yuan, Zhe cao, Shuwen Wang

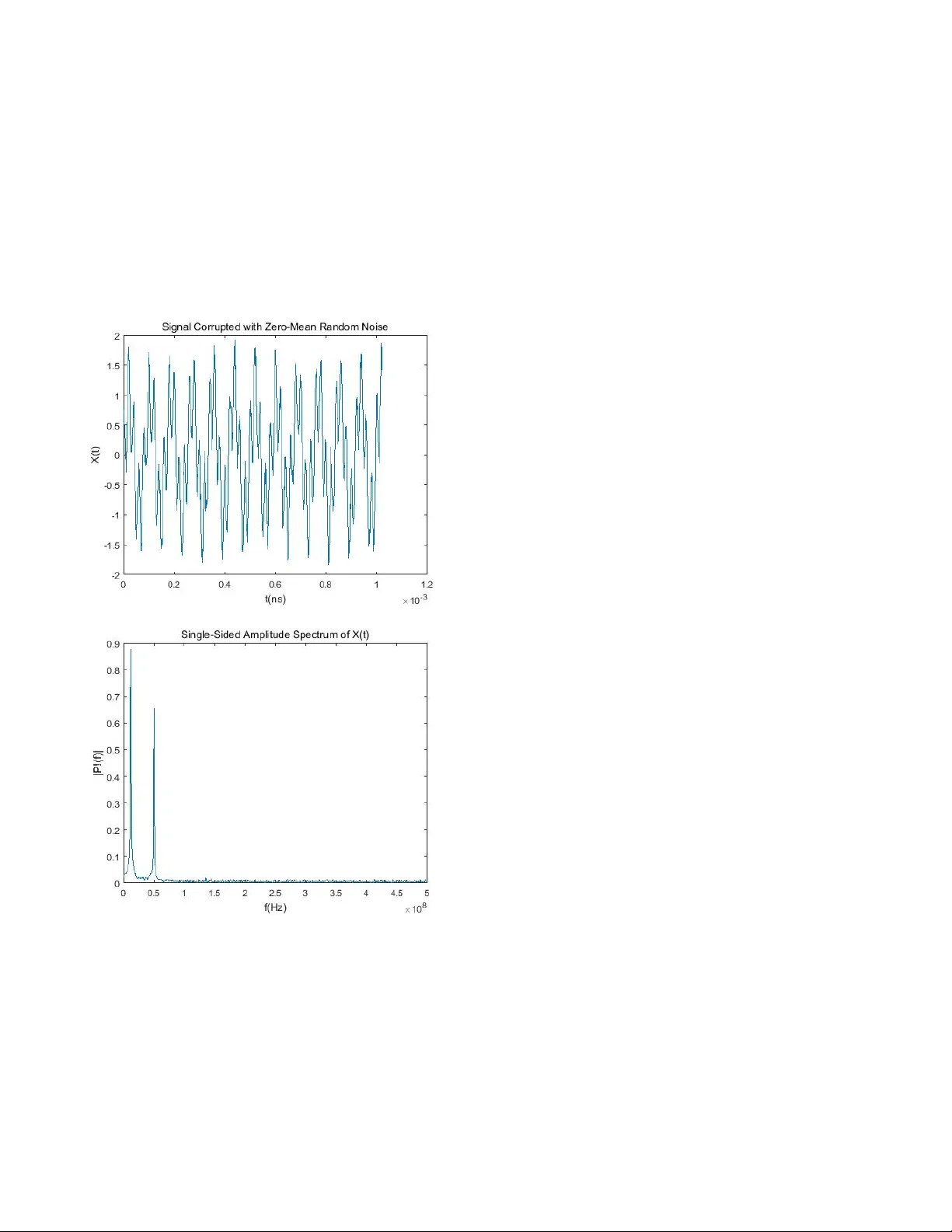

> REPLAC E THIS LINE WITH YOUR PA PER IDENTIFICA TION NUMBER (DOUBLE - CLICK HERE TO EDIT) < 1 Abstract — In rece nt ye ars, hi gh spe ed an d high re sol uti on analog -to- digital conv erter (ADC) is widely emplo yed in man y physi cal ex peri ments, es peci ally in hig h pr ecis ion t ime and char ge meas ure ment. The r api d inc reas ing amou nt of dig iti zed d ata demands faster computin g. FPGA acc eler atio n has a n attr acting prospect i n data pr ocess for i ts strea m process and parallel proc ess featu re. In thi s pa per, an ADC pe rfor ma nce cal ibr at ion applicati on based on FPGA acc elerati on is described. F PGA reads the A DC digi tize d dat a str ea m fr o m P C me mo ry , pr oc e ss es and then w rite s processed result ba ck to the PC m emory. P CIE bus is appli ed t o inc reas e th e dat a tr ansfe r spe ed, and f loat i ng poi nt algorith m is applied to i mprove the a ccuracy . The test result show s that FPGA accel eratio n can reduce t he processi ng ti m e of the AD C perf or mance c alibr ati on co mpa red w it h tradit iona l met hod of C - based C PU proce ssi ng. This fra me of P CIE - base d FPGA accel erat ion met hod can be ap plied in a naly sis and s imul ati on i n the fut ure physical experi ment for l arge ADC array, such as CC D camera a nd w avefor m digiti zation re ado ut electr onic s calibr ati on. Index Terms — ADC perfor mance , F PGA accelerati on, PCIE. I. I NTRODUCTION DC (analog - to - digital converte r) plays an i mportant role in phys ics e xper ime nts in a nalo g sig nal acquisitio n [1 ,2 ] . T he performance of ADC is very im portant for it influences the data accuracy and experiment result. Thus the calibration of ADC performance is very important. The m ost concerned dynamic parameter s of an ADC chip are SNR (S igna l - to - No ise Rati o ), SINAD (Signal to Noise and Distortio n Ratio), ENOB (Effe ctive Number of Bit s), THD (Total Harm onic Distortion) and SFDR (Spurious Free Dynam ic Range). FPGA (Field - Programmable Gate Array), for its parallel processing and st r ea m pro cessi ng str uctur e, has an at tracting feature in acceleration of data process [ 3,4 ] . The data stream can be transferred into FPGA, processed, and write back to PC memory simultaneously. The data processing speed can reach up to 2 GB/s in desi gn in FPGA . P CIE - bus based DM A (Direct Memory Access) was applied in data transmission between FPGA and PC, and floa ting point was applied to im prove the accuracy . Man uscr ipt rec eived Jun e 9 , 201 8. T his w or k w as su pport ed by the Ke y Program of t he Nati onal Na tura l S cience Foun dation of China (Gran t No. 1163500 7 ) , the Y ou ng F und Pr oj ects of the Nat iona l Na tura l Sc ie nce Fo undati on of China (Grant No. 1150518 2), and the State Key Lab oratory of Particl e D ete ction a nd El ectr onic s (N o. SK LP DE - ZZ - 2018 14). II. P RINCIPLE AND METHOD The dynamic parameters are all calculated on the base of spectrum anal ysis, mainly consisting o f FFT (Fast Fourier Tr ansfor m), which i s ver y ti me co nsu min g [5] . As FFT is calculated parallel, m eeting the feature of FPGA computing, so it is suitable to be separated and processed by FP GA. Aft er spectrum analysis, FPGA write results back to the PC memory and the program continues to calculate the parameters of ADC. PCIE Spec tr um An alysi s FPGA Re ad b uf fe r PC memo ry Wr ite b uf fe r Figur e 1. Struc tur e of dat a str eam The structure of data process stream is shown in Fig. 1. FPGA read s da t a f r o m PC me mo r y , im plem ent s spectrum anal ysis a nd the n wr ite s results back to PC mem ory . x(0) Input data x(N/2-1) x(N/2) x(N-1) …… …… Sta g e 1 Sta g e l og 2 N Sta g e l og 2 N-1 Output data X(0) X(N-2) X(1) X(N-1) …… Fig ure 2 pipel ined st rea m pro ces s. For a n N point s FFT, the amount of co mplex multiplic ation is N×log 2 N. I n the F PGA, N line s ca n run si multa neo usl y, log 2 N level was need for an N - poin t group. For a si gna l 1024 - point FFT, 4258 clocks are needed. However, as the FPGA can be conf igur ed to w ork in pi pelin e, mul ti - level operation can be carried out simu ltaneously. That is, mu ltiple group data can be processed in the same time. As shown i n Fig. 2, while d ata grou p 1 is on Sta ge log 2 N, d ata gr oup 2 i s bei ng pro cesse d in stage log 2 N- 1, and d ata gr oup N is st rea med i n on s tage 1. T he feature of parallel process and stream process result in acceleration in proc ess spee d and red uctio n in ti me . Autho rs ar e w ith the De par tmen t of Mode rn P hys ics, U nive rsity of Scienc e and T echn olo gy of Chi na, H ef ei, A nhui 230 026, Chi na. C orr espo n ding author: caozhe @ustc.e du.c n. Application of FP GA Acceleration in ADC Perfo rman ce Calibra tion Guangy uan Yuan, Zhe Cao, Shuwen W ang, Shubin Li u, Qi An A > REPLAC E THIS LINE WITH YOUR PA PER IDENTIFICA TION NUMBER (DOUBLE - CLICK HERE TO EDIT) < 2 III. V ER IFIC AT IO N TE ST The performance test of the design was carried on in Virtex - 7 XC7VX690T (Xil inx F PGA) and xe onE5 - 2609 v4 (Int el CP U). P ro grams ar e de sig ned with and wit hout FPG A separately to compare the results. A g roup dat a, cons ist of 1024 64 - bit points, was g enerated to test the perform ance of the programs. The data was generated by formula: X(t)=0 .7*cos (2*pi*50 *1000000 *t)+sin (2*pi*12 *1000000 *t)+0.1 *randn() . In program applying FPGA acceleration, one group data was carried i nto FP GA at o ne t ime . After processing, th e FPGA wrot e data bac k to PC mem ory and the program con tinue d to calculate the parameters. Figure 2. Time domai n signal wit h random Nois e. Fig ure 3. F re quency domain si gna l af te r pr oce ssing . Figur e 2 s ho ws the d ata generated by PC, consisting of a 50 MHz signal, a 12 MHz signal and ra ndom noise. F igure 3 is the resul t sho wn i n f requency domain after process . The re sults applying FPGA and pure CPU processed are the same, meeting design expectations. CPU r un s in 1 .7 G Hz while t h e s ys te m o f F P GA r un s in 250 MHz. 10^9 times are repeated to figu re out the average process time of the programs. The average t ime processed by program written in C ++ is 2.19 m s, while tha t of prog ram a pplying FPGA i s 18 u s, consi ste nt with the expected result. As a group data con sist of 1024 64 - bit point s, the c orrespon ding proce ss speed is 440MB/s. The s peed i s fas tened by more t han 100 ti me s . IV. D ISCUSSION If continuous data are provided to spectru m analysis rath er than one g roup dat a on ce, th e average processi ng time can reach up to the li mit of F FT b us spe ed, which is 2 GB/ s when the syst em clock is desi gned to 250 MH z. Besi des, m ore FFT module can be implemented in FPGA to further accelerate the speed to the li mit of PCIE bus . In addit ion, other particular data p rocess can also be accelerated by FPGA. The calculation of ENOB, SNR, SINAD, THD, SFDR and SFDR can also be done in FPGA . V. C ONCLUS ION A FP GA - based acceleration structure was introduced, spectrum analysis f or ADC calibration was performed and syste m per for mance was te st ed in o ur wor k. PC IE b us and floating point algorit hm were app lied to improve the performance. The test results shows the speed can be fastened 100 times by FPGA acceleration, while the accuracy was the same. The re sult sh ows FPGA acceleration has an at tracting feature in physical experiment data processing. Besides, the implement of spectrum analysis in FPGA can be applied in on - board calibration for large ADC array, such as CCD camera calibratio n . R EFERENCES [1] R.H. Wal den, “ An alo g - to - digital co nve rte r s urvey and analy sis ”, IEEE Jour nal o n Se le cted A reas in Co mmu nica tio ns , vol. 17, pp . 539 - 550, A pr . 1999. [2] R.H. W alden, “ Performan ce trends for analog to digit al converters ”, IEEE Commun ication s Magazine, vol. 37, pp. 96 - 101, Feb. 199 9. [3] A, Go thandaram an, et al . “F PGA acce leration o f a qua ntum Mo nte Carl o applic atio n ”, Vol. 34, pp .278 - 291, Ma y . 2008. [4] J.P. Wal ters, e t al . “ MPI - HMMER - Bo ost: Distri bute d F PGA Acce lera tion ”, The Journ al of VLSI Signa l Process ing S ystems for S ignal, I mage , and Vide o T echno lo gy . Vol. 48, pp. 22 3 - 238, Sep. 200 7. [5] W.T. Cochran, et al. “ W hat is the fast Fourier tran sform? ”, Proceedings of the I EEE , Vol. 5 5, pp. 1664 - 1674, Oct . 1966 .

Original Paper

Loading high-quality paper...

Comments & Academic Discussion

Loading comments...

Leave a Comment