온칩 CIC 디지털 디시메이션 필터 설계 및 구현

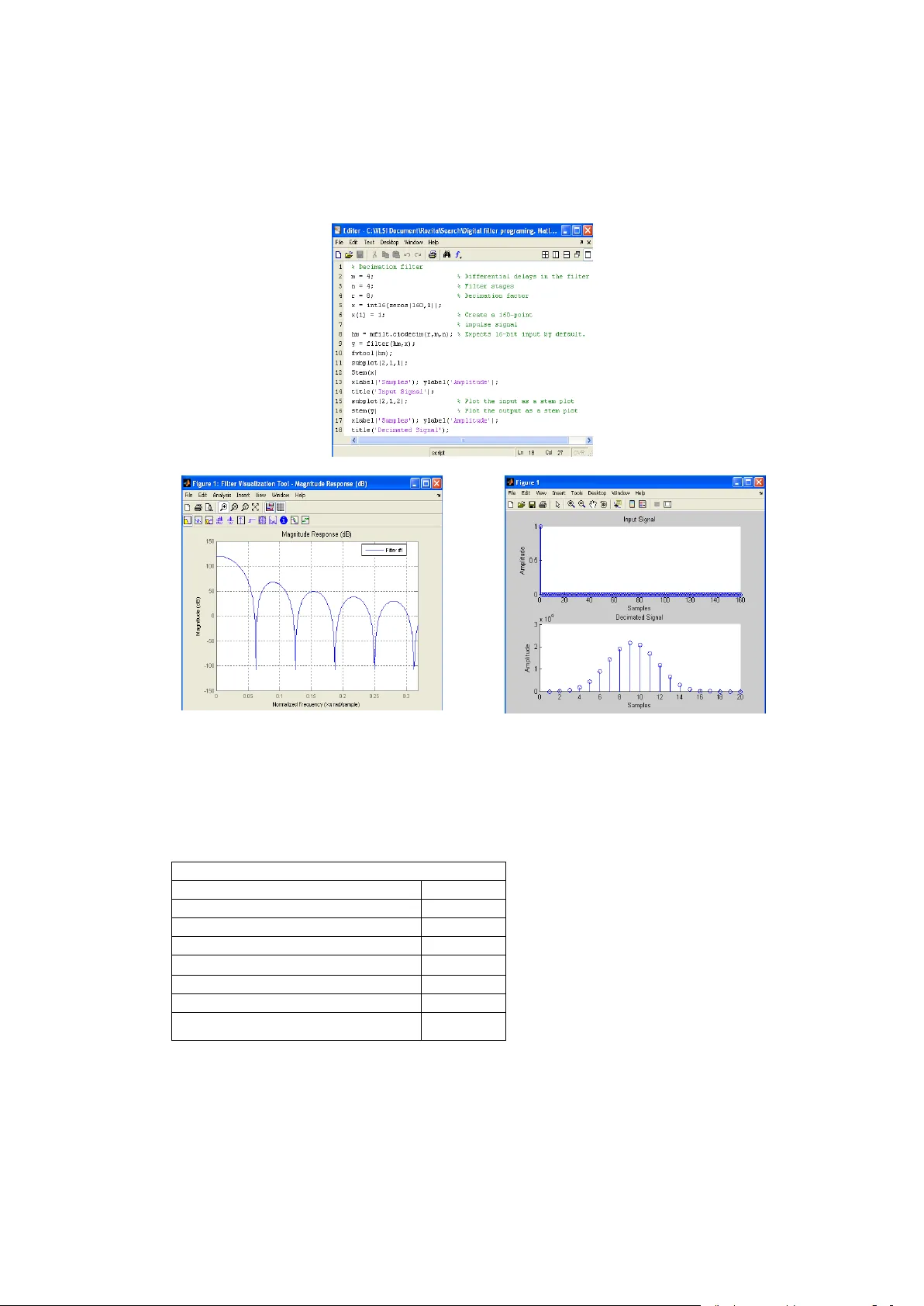

본 논문은 저전력·저복잡도 특성을 갖는 캐스케이디드 적분‑콤(CIC) 필터를 설계하고, MATLAB Simulink를 이용해 기능을 검증한 뒤 FPGA 기반 온칩 구현을 위한 기본 구조와 핀 인터페이스를 제시한다. 200 kHz 입력을 4 kHz 출력으로 50배 디시메이션하며, 2단 적분‑콤 구조와 차동 지연 1을 사용한다. 통과대역 감쇠와 별도 FIR 보상 필요성을 논의하고, 워드‑길이 제약식도 제시한다.

저자: Rozita Teymourzadeh, Masuri Othman

본 논문은 고해상도 ΣΔ 변조기에서 발생하는 고속 1‑bit 데이터 스트림을 저속 다비트 데이터로 변환하기 위한 디시메이션 단계로 캐스케이디드 적분‑콤(CIC) 필터를 선택하고, 그 설계·시뮬레이션·온칩 구현까지 일련의 과정을 상세히 기술한다.

첫 번째 섹션에서는 ΣΔ 변조기의 오버샘플링 특성과 디시메이션 필요성을 소개하고, CIC 필터가 곱셈 연산이 필요 없는 단순 구조(적분기와 콤 단계만)로 전력·면적 효율이 높으며, 필터 계수가 모두 1이므로 저장 공간이 필요 없다는 장점을 강조한다.

두 번째 섹션에서는 CIC 필터의 기본 수학적 모델을 제시한다. 적분기 y

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기