On-Chip Implementation of Cascaded Integrator Comb filters (CIC) for DSP applications

This paper presents the design of CIC filters based on a low-pass filter for reducing the sampling rate, also known as decimation process. The targeted application for the filter is in the analog to digital conversion (ADC).The CIC is chosen because …

Authors: Rozita Teymourzadeh, Masuri Othman

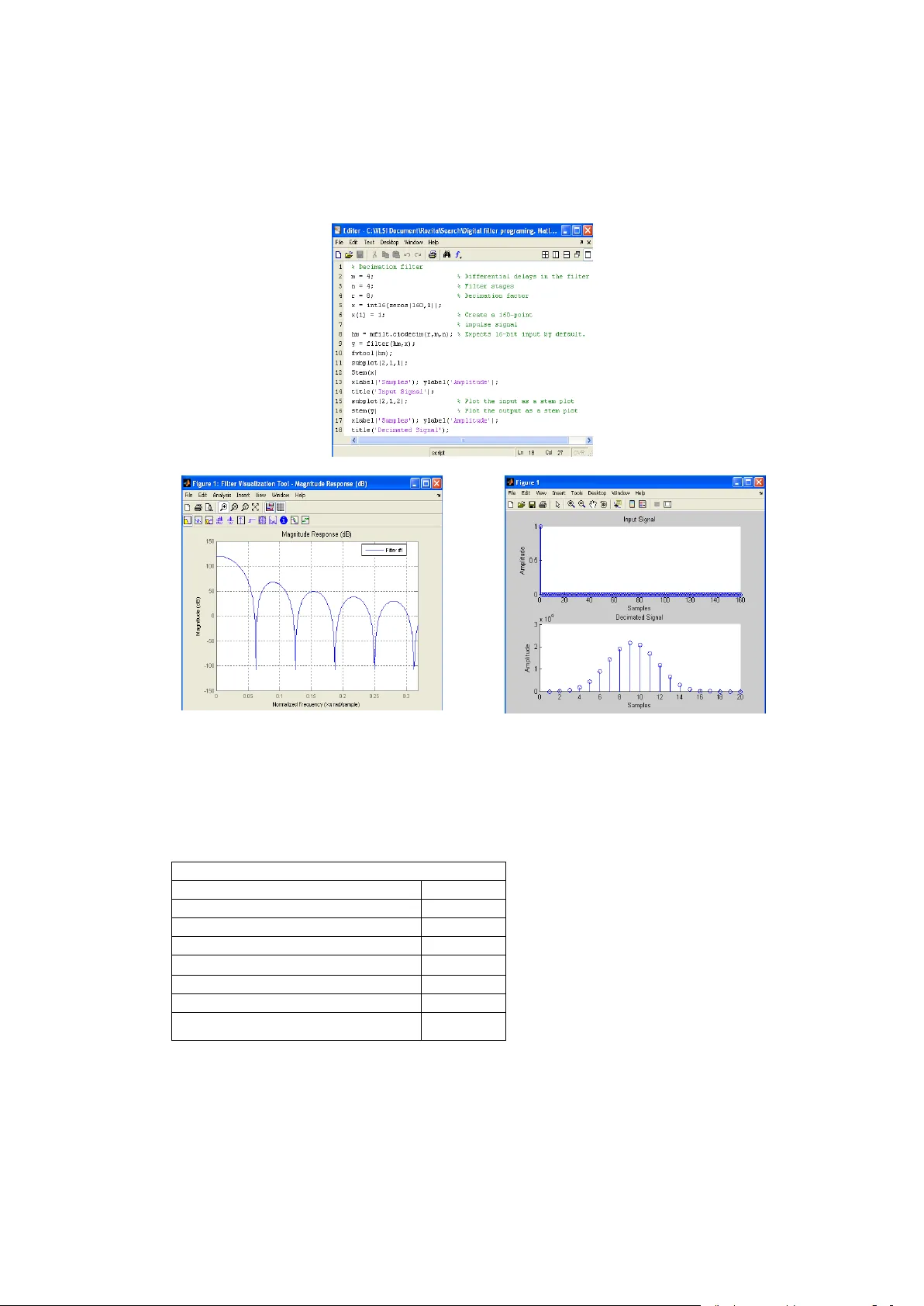

On -Chip Implementation of Cascaded Integrated Comb filters (CIC) for DSP applications Rozita Teymourzadeh & Prof. Dr. Masuri Othm an VLSI Design Centre BlokInovasi2, Fakulti Kejuruteraan, University Kebangsaan Malaysia 43600 UKM, Bangi, Selangor DE, Malaysia E-mail: rozita60@vlsi.eng.ukm.m y Abstract - T his paper presents the design o f a CIC filters ba sed on a low -pass filter for reducing the sampling rate, also kno wn as decimation proce ss. The targeted applicatio n for the filter is in the a nalog to digital conversion (ADC).The CIC is c hosen because of it s attractive property of both low power and co mplexity since it dose not required multipliers. Simulink too lbox available in Matlab software is used to design and simulate the f unctionality of the CIC filter. This paper also shows how sample freq uency i s decreased by CI C filter and it can be used to give enough stop -band attenuation to prevent aliasing after deci mation. Keyword – CI C, co mb, Filters , Converter s , Si gma Delta A/D co nversion; co mb filters, decimation filters I. INTROD UCTION Sigma delta (∑ Δ) modulator is an o ver sampled modulation tec hnique which provides high reso lution sample outp ut in contrast to the s tandard Nyquist samplin g tec hnique. However at the output, the sampling process is nee ded in ord er to bring do wn the high sampling freq uency. T he CIC filter is a pr eferred technique for this purpose. Additionally the CIC filter d oes not require stor age for filter coef ficients and multipliers as all coefficients are unit y [1]. Furthermore it s o n-chip impleme ntation is efficient b ecause of its regular structure co nsisting o f two basic build ing blocks, minimum external co ntrol and less complicated loca l timing is required and its change factor s is reconfigurable w ith the addition of a scali ng circuit and minimal cha nges to t he filter timing. The CIC filter also removes q uantization noise and prevents aliasing intro duced during sampli ng r ate decreasing. In this project, the desi gn and i mplementatio n of CIC filters, it s impulse responses ar e e val uated b y using Matlab. Once the functionality of the filter is verified, the Verilo g cod ing for the filter will be writte n, simulated and co mpared with the results from the MATLAB simulations. The chip implementatio n of the filter will follow. Section II presents o verview of the CIC filter follo wed b y section II I which gives so me res ults of the characteristics o f the filters. Chip i mplementation of the filters is described in the last section. II. An overv iew of CIC filters A. CIC filters to perform the decim ation process. The purpose of the CIC filter is twofold; firstly to remove filtering noise whic h could be aliased back to the b ase band signals a nd seco ndly to co nvert hig h sa mple rate 1 -bit dat a stream at the output of t he Sig ma-delta modulator an n-bit data strea m with lower sample rate ( where n is determined b y the speci fications of the filters). T his pro cess is also known as deci mation which is e ssentiall y performing the avera ging and a rate red uction functions simultaneously. Fi gure 1 sho ws the d ecimation p rocess using the CIC filter ( Block in t he middle). Fig.1: Digital Decimatio n Process This CIC filter chosen is a lo w pass filter with sy mmetric co efficient value and linear - phase response. It p rovides 4:1 decimation (in above example) and magnitude compensation for the magnitude change (droop) from the CIC filter output. Detailed analysis will be pr esented in in section IV. B. CIC filters equa tion and block dia gram The building blocks of t he CIC filter are the integrator (Fig. 2) and the comb filter (Fig. 3). For the integrator, its equation in the discrete -time do main and z-do main are: y[n] = y[n-1] + x[n] 1(a) H I (z) = 1 1 1 z 1(b) Which is a si mply single-pole IIR filter with a unity feedback coefficient and in other words a single integrator by itself is unstable. The com b f ilters (anot her part of CIC filter) w hich d oes n ot require f eedback for M (differential dela y) = 1 is shown below: Sampling rate red uction b y t he comb filter is give n by fs/R where Fs is t he high sampling rate and R is the deci mation factor of the filter, the op eration of the comb filter is: y[n] = x[n] - x[n -RM] 2 (a) Fig.3: Comb Cell Fig.2: Integrator Cell H C (z) = (1 -z RM ) 2 (b) The transfer function after ad ding Comb and Integrator block and in N sta ge is given as: H (z) = H N I (z). H N C (z) = 1 0 1 ) ( ) 1 ( ) 1 ( RM k N k N N RM z z z (3) The block diagram of one sta ge CIC filter is dra wn as below: Fig.4: One-stage CIC filtering P rocess The gain of the CIC filter can be expressed as: G = (RM) N ( 4) III. IMPLE MENTATIO N A. Simulation The structure of the CI C filter in figure 4 is inputted to Simulink toolbox as sho wn below: Fig.5: CIC filter simulation Input and output o f simulations (fig.6) make clearer the CIC filter tasks. Input freq uency is 200 kHz and output frequenc y is 4 kHz which give dec imation factor o f 50. B ecause of the I ntegrator b lock i n CIC filter DC gain also has increased and it evaluated by Gain equation: G = (50 × 1) 2 = 2500 So output signal should be have 2500 v DC gain. B. Impulse and Freq uency Respons e Overall filter transfer functio n of N -order CIC w ith gain involvin g can be expressed as : H(z) = N D K k N N D N z z z D 1 0 1 ) 1 ( ) 1 ( 1 (5) Where the term 1/D N takes in to account the DC gain o f the in tegrators and D = RM is desired deci mation factor. CIC filters have a linear -phase low-pass frequency response that can be obtained by setting z = e j (by assuming a sampling interval T = 1 / f s , the digital freque ncy f d is related to ω thro ugh ω = 2π f T = 2π f d , where f is the analog freq uency, obtaining H(e d f j 2 ) = N D 1 2 1 2 ) ) ( ) ( ( D N d j N d d d e f Si n Df Si n (6) The trans fer function o f equatio n (6) is eq ual to zero at integer multiples o f the frequenc y f k = k.(1/D), with k = 1,…,[ D/2 ] if D is even and k = 1 ,…,[ D-1/2 ] for D odd.[2] Fig.6: Input and Output CIC filter Impulse response and tran sfer function detect some of the character istic o f CIC filter for example CIC filter in fig. (7) is stable becau se its imp ulse r esponse h( n) decays to 0 as n goes to infinity. Impulse response has b een sho wn in fig. (7) by using Matlab soft ware: Fig.7: Impulse response Unstable f ilters are not no rmally useful in practice because their output grows exponentially and its energ y is not limited. Fig(8) detects ho w CIC filter dec reases 160 samples to 20 samples b y decimation facto r equal 8 and also freque ncy resp onse for a mention filter with M=4, N=4 & R=8 are shown as below: Fig.8: Matlab Pro gramming for frequency and I mpulse response IV. SPECI FICATION & PASS BAND DROOP A. Specification CIC filter is equivalent to NFI R filter. Specification of CI C filter has been chosen as tab le (1): Application Function amount N – Number of stages 2 R – Deci mation factor 50 M – Differential Delay 1 F s - sample frequenc y 200 kHz Fc - band width 4 kHz F AI - Aliasing/imaging atten uation 20.9 dB Pass band attenuation at Fc (d B) 1.82 dB Tbl.1: Specificat ion of CIC filter The n umber of stage in t he filter deter mines t he pas s b and atten uation, Increasing N improves filter ab ility to rej ect aliasing b ut it al so increases droop (or roll off) in the filter pass band.[3] Differential del ay is used as a design para meter to contro l the placement of the nulls. For CIC deci mation filters t he region around every Mth null is folded in to the pass band causing aliasing error s. Differential d elay is a filter design para meter used to control the frequency respo nse of filter is restricted to be either 1 or 2. [4] B. Pass band droop i n CIC filter CIC filters are multiplier les s structure, co nsisting of o nly add ers, sub tractors and register. CIC filter increases droop in pass ba nd freq uency a nd al so increasing number o f sta ge increases atten uation at frequency in the locality o f the zero. T he increases droop may no t be acceptable in ap plication. d roop is frequentl y corr ected usin g a n additional (no n -CIC- based) stage of filtering after the CI C deci mator. [4] B ecause o f t he pass ba nd droop and therefore narrow usable p ass band in CIC filter, many CIC designs utilize an add itional FIR filter at the low sampling rate. Filter sharpening can be used to i mprove the r esponse of CIC filter. This filter will equalize pass band droop and perform a lo w rate change usually by a factor of two to ei ght. ( CIC filter + Co mpensation filter= composite filter) Fig.9: Pass band co mpensation by FIR filter FIR filter or a co mpensation filter (not part o f CIC core) can b e used to flatten t he pass band frequency response. F or a CIC d ecimator compensation filter operates at the decimated sample rate. Using an appro priate FIR filter i n ser ies after the CIC decimatio n filter can compensate for the i nduced droop . V. CI C FILTER C ONSTRAIN TS & CHIP D ESIGN A. CIC filter cons traints CIC decimator filter have t he following two constraints: The word lengths of the filter stages must be no increasing. T hat is the w ord length of each filter stage. T he number of bits of the first filter stage must be greater than or equal to the quantity B max. [5] . Bmax is achieved b y followed equation : Bmax = [N log 1 2 B RM ] (7) Where B is the number of bits of the input. The number of output bit in l ast comb stage is ac hieved as belo w: Bout = [N log B RM 2 ] (8) Bout bits are nee ded for each in tegrator and com b stag e. B. Chip design For designing a CIC filter as a chip at FPGA, some pins are needed on it. A simple simulation of this chip ha s been showed in figure (1 0): CLK: Clock master cloc k is input pin and bec ome active by r ising edge. Din: Data input is i nput pin and also is B -bit wide filter i nput port. ND: New Data is Active high and input pi n. Whe n thi s sig nal is asserted the data sa mple presented on the Din por t is loaded in to the filter. Dout: filter output sa mple is output pin. W -bit wide filter output sample bus. Fig.10: CIC filter Chip RDY: filter output sa mple read y is Ac tive high output pin . Indicates a new filter output sample is available on the Do ut port. RFD: Read y For Data is active high o utput pin. Indicates when the filter can ac cept a new input sample. LDin: LDin i nput bus is i nput p in and used to suppl y the s ample rate cha nge va lue whe n the programmable rate chan ge option for the CIC deci mator is selected. WE: W rite Enab le signal is active high input p in. T his sign al is associated with the LDin port.. This example o f CIC filter chip is a basic example and the str ucture of its actio n has b een considered as chart which has been shown as belo w: Mention chart sho ws how pins of chip act together till Dout become read y in output port. CIC decimation timing has been s howed i n below figure. In this figure new data sa mple has been considered to supply to the chip on ever y clock cycle. Dout also beco me ready after passing some clock p ulse inter val depends on f ilter late ncy and R and after that next D out become read y after R clock cycle. Fig.11: CIC filter Chip Fig.12: CIC decimation t iming The time interval is a function of the do wn-sampli ng factor R and a fixed latency t hat is related to internal pipeline reg isters in the CIC chi p. T he number of pipeline stages depends on the chip custo mization para meters.[4] VI. CON CLUSION In this paper structure, block diagram a nd speci fication of CIC filter b y using Matlab software has been prop osed and also first step of c hip implementation w a s described. Although the obj ective of this paper has been written b ut further work ab out truncatio n or rounding which may be used for each stage still has not b e done b y th is paper . VII. A CKNOWLEDG EMENT I wish to thank my supervi sor, Prof. Dr. Masuri Othman who has assisted me for completion of this dissertatio n. VIII. REF ERENCES [1] Hogenauer EB, ( 1981). An economica l cla ss o f digital filters for decimation and interpolation, IEEE transactions o n aco ustic, speech and signal processing, Sunnyvale, CA . Assp-29(2):1 55162 [2] Fred Daneshgaran & Massimiliano Laddo mada, (2002). A novel class of dec imation filters for sigma delta A/D converters, W irel. Commun. Mo b. Comput, 867 - 882. [3] Matlab So ftware, (2004). Mfilt.CI Cdecim , filter design t oolbox. [4] Xilinx, ( 2002). Lo gic Core Cascaded I ntegrator-Comb (CIC) filter V3 .0, P roduct specification. [5] Matlab So ftware, (2004). CIC decimation. Signal processing Blockset.

Original Paper

Loading high-quality paper...

Comments & Academic Discussion

Loading comments...

Leave a Comment