멤리스터 기반 가우시안 필터 설계와 구현

본 논문은 아날로그 도메인에서 가우시안 필터를 근사하기 위해 멤리스터와 RLC 회로를 활용한 설계 방법을 제시한다. 초기에는 인덕터를 포함한 사다리형 네트워크를 시뮬레이션했으나, 인덕터의 실용적 제약으로 8차 Sallen‑Key 구조로 전환하고 모든 저항을 멤리스터로 교체하였다. 최종 회로는 4.78 Hz의 차단 주파수와 –135°의 위상 특성을 보이며, 멤리스터의 가변 저항성을 통해 필터 파라미터 조정이 가능함을 확인하였다.

저자: Alex Pappachen James, Aidyn Zhambyl, Anju N

본 연구는 아날로그 도메인에서 가우시안 필터를 근사하기 위한 회로 설계 방법을 탐구한다. 가우시안 필터는 입력 신호와 가우시안 함수의 컨볼루션으로 정의되며, 이미지 처리와 디지털 통신에서 잡음 억제와 대역 제한에 널리 사용된다. 전통적으로는 디지털 구현이 주류였지만, 아날로그 구현이 필요할 경우 정확한 임펄스 응답을 재현해야 한다. 이를 위해 저자는 두 가지 설계 접근을 제시한다.

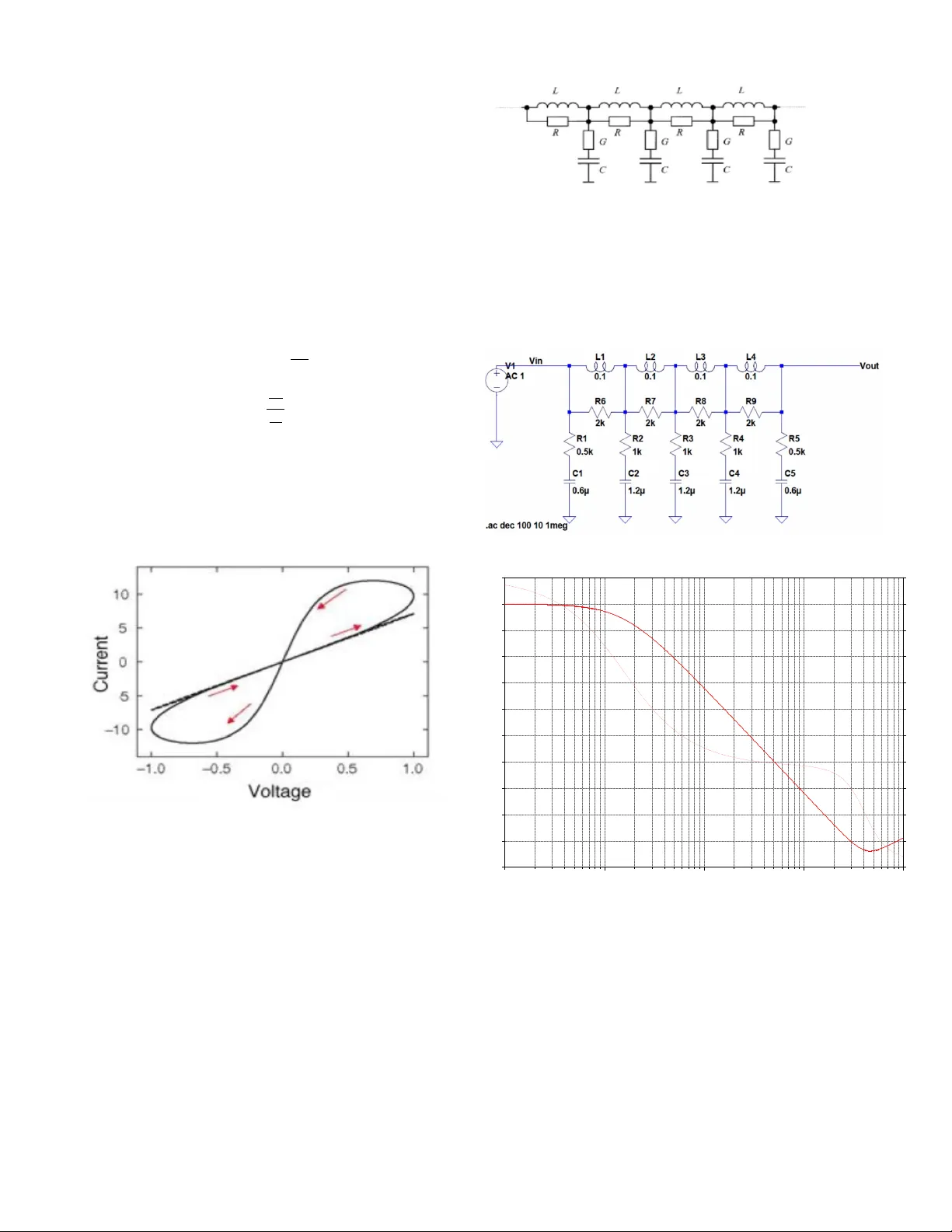

첫 번째 접근은 기존 연구에서 제시된 사다리형 전송선 모델을 그대로 차용한 것이다. 회로는 9개의 저항(R1~R9), 5개의 커패시터(C1~C5), 4개의 인덕터(L1~L4)로 구성되며, 각 소자의 값은 R = 0.5–2 kΩ, C = 0.6–1.2 µF, L = 0.1 H로 설정하였다. SPICE 시뮬레이션 결과, 주파수 응답이 가우시안 형태에 근접했으나, 인덕터 사용으로 인한 물리적 구현상의 제약(크기, 자기 간섭, 손실 등)이 지적되었다.

이에 저자는 인덕터를 제거하고, 8차 Sallen‑Key 토폴로지를 채택한 두 번째 설계로 전환한다. Sallen‑Key 구조는 저역통과 필터를 고차 필터와 동일하게 구현할 수 있는 장점이 있다. 회로의 모든 저항을 멤리스터로 교체함으로써, 저항값이 전류 흐름에 따라 히스테리시스적으로 변하는 특성을 활용한다. 멤리스터는 전압-전류 히스토리 루프를 형성하며, 전력 소모가 낮고 CMOS와 호환성이 좋다.

시뮬레이션 결과, 8차 멤리스터 기반 Sallen‑Key 회로는 차단 주파수 f_c ≈ 4.78 Hz, 위상 이동 –135°를 보이며, 전송 함수 H(s) = (0.2s³+1.2s²–5s+40)/(2.9s⁴+12s³+27.4s²+34s+19)와 일치한다. 이는 이론적인 가우시안 필터 특성과 충분히 근접한다. 또한, 멤리스터의 가변 저항성으로 인해 필터 파라미터(차단 주파수, 이득 등)를 실시간으로 조정할 수 있는 가능성을 제시한다.

논문은 설계 과정에서 얻은 데이터 포인트를 이용해 로그 함수를 통한 근사식 y = –9.087 ln(x)+38.758 (x: 주파수, y: dB)도 제시했지만, 데이터 포인트 수가 적어 정확도가 떨어진다고 언급한다.

결론에서는 인덕터 없는 설계가 실용적이며, 멤리스터 도입으로 필터의 민감도와 조정 가능성이 향상된다고 강조한다. 다만, 멤리스터의 비선형 동작, 전압 의존성, 온도 및 공정 변동에 대한 상세 분석이 부족하므로, 향후 연구에서는 다양한 입력 전압에서의 저항 변화, 전력 소모, 잡음 특성, 그리고 PCB 레이아웃에서의 기생 요소 영향을 평가해야 한다고 제안한다. 이러한 추가 연구가 이루어지면, 저전력 이미지 처리, 무선 통신, 바이오 신호 처리 등 다양한 분야에서 멤리스터 기반 아날로그 가우시안 필터의 적용 가능성이 크게 확대될 것이다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기