Cavity Simulator for European Spallation Source

European Spallation Source will be the brightest neutron source in the world. It is being built in Lund, Sweden. Over 120 superconducting cavities will be installed in the facility, each regulated by an individual LLRF control system. To reduce the r…

Authors: Maciej Grzegrzo{l}ka, Krzysztof Czuba, Mateusz Lipinski

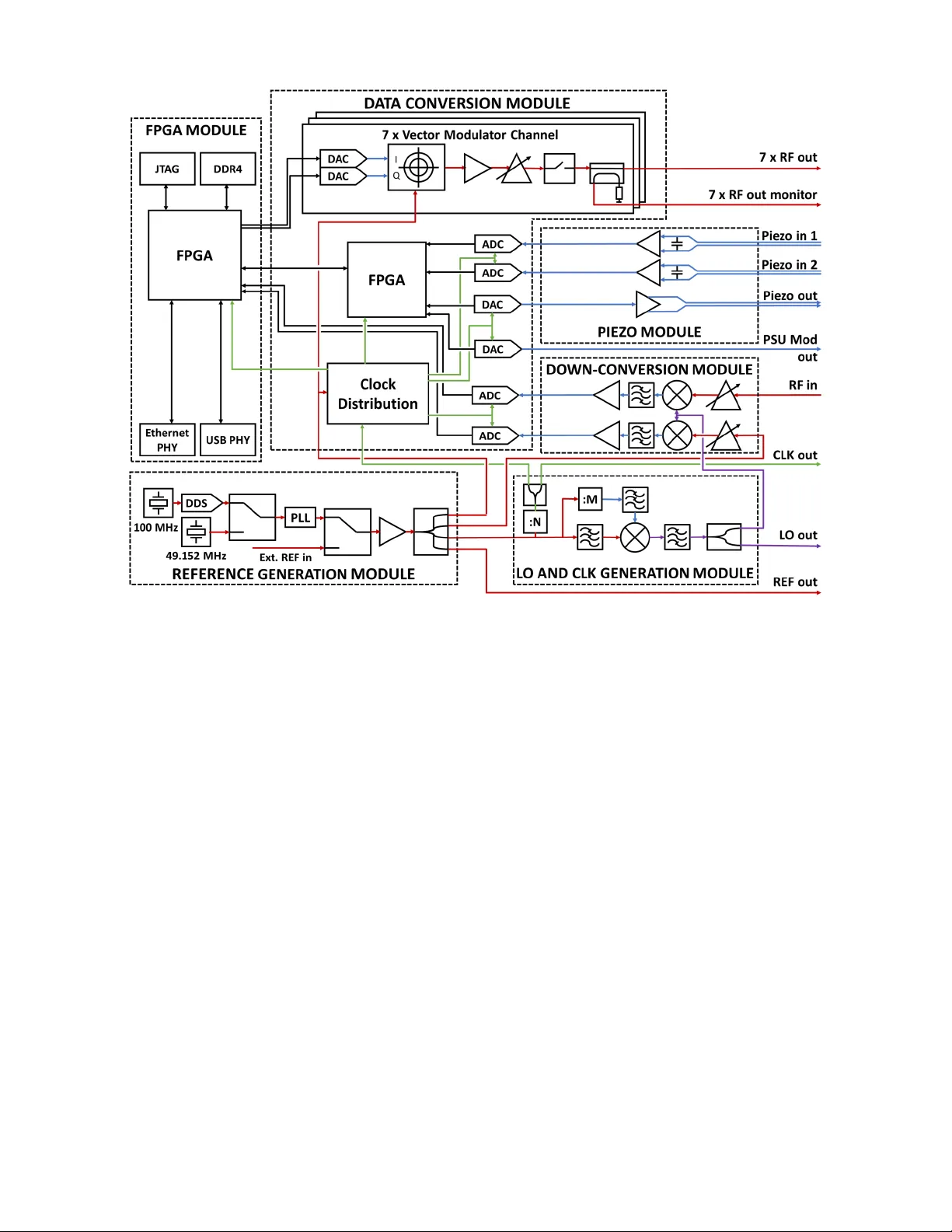

1 Ca vity Simulator for European Spallation Source Maciej Grzegrz ´ ołka, Krzysztof Czuba, Member , IEEE, Mateusz Lipi ´ nski, and Igor Rutko wski, Abstract —European Spallation Source will be the brightest neutron source in the world. It is being b uilt in Lund, Sweden. Over 120 superconducting cavities will be installed in the facility , each regulated by an individual LLRF control system. T o reduce the risk associated with testing the systems on real ca vities a Cavity Simulator was designed. It repr oduces the beha viour of superconducting cavities used in the medium and high beta sections of ESS’ s Linac. The high power RF amplifier and piezo actuators parameters are also simulated. Based on the RF drive and piezo control signals the Cavity Simulator generates the RF signals acquired by the inputs of the LLRF control system. This is used to close the LLRF feedback loop in real time. The RF front end of the Cavity Simulator consists of vector modulators, down-con verting circuits, and a set of fast data conv erters. The cavity response simulation is performed in a high speed FPGA logic by a dedicated firmware, that was optimized to minimize the processing time. The device also generates clock, LO, and the 704.42 MHz r eference signals to allow f or system tests outside of the accelerator envir onment. In this paper the design of the Cavity Simulator , description of the algorithms used in its firmware, and measurement results of the device are presented. Index T erms —Accelerators, European Spallation Source, RF systems, Cavity Simulator I . I N T RO D U C T I O N M EDIUM and high beta sections of European Spalla- tion Source linac will consist of 120 superconducting elliptical cavities operating at 704.42 MHz [1]. Each of these cavities requires an indi vidual lo w level radio frequency (LLRF) control system. Lund University and ESS design the architecture of those systems [2]. They are partnered by Polish Electronics Group (PEG), which dev elops three of the system’ s component and will also assemble, test, and install the systems in the ESS facility [3]. T esting the LLRF control systems with the real cavities is very risky and in can result in an expensi ve damage. T o mitigate this risk, PEG dev elops the Cavity Simulator which is a device that reproduces the behavior of the real superconducting ca vity driv en by a high po wer amplifier . It will be used to test all 704.42 MHz LLRF control system units before they are commisioned with real cavities. This device can also be used for the dev elopment of LLRF system’ s algorithms and firmw are. Among others, the de vice simulates following phenomena: cavity dynamics, ca vity detuning, piezo compensation, Lorentz force detuning, beam loading, microphonics, amplifier non- linearity , and amplifiers PSU modulator influence. Fig. 1. presents the simplified schematic of the simulated devices and their connection to the LLRF control system. Maciej Grzegrz ´ ołka, Krzysztof Czuba, Mateusz Lipi ´ nski and Igor Rutko wski are with W arsaw University of T echnology (WUT), W arsaw , Poland.. Manuscript receiv ed June 24, 2018 Fig. 1. Scope of the simulation. The simulation model is implemented inside a high- performance FPGA logic, which is combined with a set of data con verters and a dedicated analog front-end connecting the Cavity Simulator and the LLRF control system. The simulation parameters can be set on-line through an Ethernet network. The 704.42 MHz superconducting cavities installed in the Medium and High Beta sections of the ESS Linac are de- scribed in [4]. T able I lists the essential parameters of those cavities. Sev eral cavity simulators hav e been dev eloped by , e.g., DESY , LBNL, and KEK [5]–[7]. The y focus mostly on verifying the algorithms used in the LLRF control systems. The Ca vity Simulator presented in this paper allows testing the complete LLRF control system including analog circuits like, e.g., Piezo Dri ver and ADC frontend. This paper has been di vided into three parts. The first part presents the Ca vity Simulator’ s hardware design. The firmw are and simulation model description follow it. In the final part, the measurements results are sho wn. T ABLE I B A S I C P AR A M ET E R S O F T H E C A V I TE S U S ED I N T H E M E D IU M A N D H I G H B E T A S EC T I O NS O F T H E E S S L I NAC . Parameter Medium Beta High Beta Nominal Accelerating Gradient (MV/m) < 16.7 < 19.9 Number of Cells 6 5 Q 0 > 5e9 > 5e9 Q ext 7.5e5 7.6e5 Maximum r/Q ( Ω ) 394 477 π and 4 π /5 modes seperation(MHz) 0.54 1.2 2 Fig. 2. The block diagram of Cavity Simulator’ s hardware. I I . H A R D W A R E The primary purpose of the Cavity Simulator‘s hardware is to digitize and generate RF as well as baseband signals. It is also used to produce the reference, LO, and clock signals for the LLRF control system. Additionally , the USB and Ethernet communication interfaces are provided. The device is combined of seven different modules. Fig. 2 presents the block diagram showing the structure of the hardware (without the Power Supply Module). A. FPGA Module A vast number of high-performance FPGA modules is av ailable on the market, so to reduce the design time and cost it was decided to use an of f-the-shelf component. Xilinx KCU105 board was selected due to a high number of IO pins av ailable and inte grated USB and Ethernet PHYs. B. Data Con version Module The Cavity Simulator requires many different data con vert- ers. All of them are located on the Data Con version Module, which communicates with FPGA module through two FMC connectors. In total four analog signals are digitized: RF dri ve, RF reference, and two piezo drives. The RF signals are typically detected in one of 3 ways: • direct sampling, • down-con version, • analog IQ demodulation. It was decided that the best method to adopt for this project was using the down-con version scheme. It is typically the best in terms of performance but requires additional LO generation circuit, which would hav e to be integrated into the Cavity Simulator nev ertheless. The down-con verter circuit is designed as a separate module and tw o 16-bit 250 MSPS ADCs are used to sample the intermediate frequenc y (IF) output signal. The piezo driv e signals hav e a bandwidth in a range of tens of kHz. They can be sampled directly without any frequency con version circuit, but due to a high voltage, analog front-end with additional protection is required. T wo 18-bit 5 MSPS ADCs digitize the piezo dri ve signals. The Cavity Simulator generates eight analog signals: 6 RF , piezo sensor and a amplifier PSU modulator output. Last two signals do not require any sophisticated front-end and can be generated directly by the D A Cs. The RF signals are generated using vector modulator circuits. For the best performance, it requires precise length matching of I and Q signal paths, which cannot be achiev ed using a cable connection. Therefore the vector modulator together with D A Cs is integrated into the Data Conv ersion Module. Additional 7th RF output was added to the design. It can be used for the Cavity Simulator dev elopment and testing. The Data Conv ersion Module is also equipped with a low- 3 cost FPGA. It is used to configure all ICs used in the module and to serialize the data from data conv erters operating on piezo and PSU modulator signals. C. Down-con version Module This module lowers the frequency of the input RF signals to a range suitable for the ADCs. It integrates two down- con version channels, which are based on an activ e mixer . Each channel has indi vidually controlled gain. Additionally , the mixer’ s LO signal power lev el can be controlled and optimized for the best noise performance. D. Piezo Module The amplitude of the piezo driv e signals coming from the LLRF Control System can reach 200V . Such voltage can damage the Cavity Simulator’ s electronics. The Piezo Module lowers the voltage of the piezo signals 100 times and provides additional protection circuit that should withstand the voltages up to 1kV . The piezo module also simulates Noliac N AC 2022 H30 piezo used in medium and high beta cryomodules. At cryo- genic temperatures, the capacitance of this actuator is around 2.2 µ F . The Piezo Module also inte grates one output channel sim- ulating the piezo working as a detuning sensor . This output is also protected against the high voltage because the Piezo driv er used in the ESS’ LLRF control systems shares the same connector for both piezo actuator and sensor modes of operation. E. Refer ence Generation Module Reference Generation Module distributes the 704.42 MHz RF reference signal, which can be provided externally or internally produced by this module. The generation circuit utilizes a PLL with an integrated VCO. The PLL circuit can be driv en by either 49.152 MHz crystal based generator or a DDS operating with 100 MHz clock. Such configuration allows the module to operate in one of 3 modes: • generating 704.51 MHz directly from crystal generator signal, • generating 704.42 MHz from crystal generator signal using fractional mode of the PLL, • generating 704.42 MHz from 22.013 MHz signal pro- duced by DDS. The first option offers the best phase noise performance (78.3 fs jitter in the 10 Hz to 10 MHz integration bandwidth) but has a frequenc y offset of around 100 kHz from the nominal ESS’ RF reference frequency . It is negligible for most applications (under the assumption, that LLRF system uses the same reference signal). In a case where exactly 704.42 MHz frequency is required the second and third options can be used. F . LO Gener ation Module This module is responsible for generating the LO and Clock signals. The generation scheme is based on direct analog synthesis. The clock frequency is set to 117.4 MHz, and two LO frequencies can be produced: 729.58 and 736.44 MHz. A more detailed description of this module can be found in: [8]. G. P ower Supply Module The Power Supply module po wers all other boards used in Cavity Simulator with +12V . Its primary function is condition- ing the v oltage coming from an off-the-shelf A C-DC con verter . Additionally , this module supervises the po wering sequence, monitors the po wer consumption and adjusts the cooling fans speed. H. Mechanical Design The Cavity Simulator is integrated into custom 19” rack enclosure. The boards are placed on two floors. On the top FPGA and Data Con version modules are located. The other modules, including the A C-DC con verter , are installed on the lower level. Fig. 3 shows the interior of the Cavity Simulator . Fig. 3. Interior of the Cavity Simulator . I. Har dwar e tests The hardware design was tested, and its proper operation was confirmed. The phase noise spectra of the RF reference, LO, and one of the RF outputs signals was measured (see Fig. 4). No major interference or additional noise sources were found. The spurs at 42 Hz and 90 kHz offsets are probably originating from the Agilent E5052B Signal Source Analyzer that was used for the measurement. The spur visible in the LO signal’ s phase noise at 1.1 MHz offset is caused by the DC-DC con verter located on the LO Generation Module. Fig. 4. Phase noise spectra of the RF reference, LO and RF output signals. 4 Fig. 5. The block diagram of Cavity Simulator’ s firmware. I I I . F I R M W A R E T wo FPGAs are used in the design. The firmw are for the one located on the Data Conv ersion Module integrates only basic functions like, e.g., SPI and I2C controllers and it will not be described in detail. The firmware for the FPGA Processing Module (see Fig. 5) is much more complicated, and it is responsible for: • communication through USB and Ethernet interf aces, • gathering data from ADCs, • sending data to D A Cs, • data acquisition, • digital signal processing for cavity simulation. A Xilinx MicroBlaze softcore microprocessor is used for communication with external systems. It is running a cus- tom software responsible for the interpretation of the control commands sent to the device, setting the parameters of the simulation, and readout of the recorded data stored in the DDR4 memory . A trigger signal is required to synchronize the Cavity Simulation with the LLRF control system. It can be generated locally , or an external signal can be used. It is fed to the amplifier and ca vity model and data acquisition blocks. An arbitrary waveform generator driving the additional, 7th RF output is implemented in the firmware. This tool can be used to verify the proper operation of the Cavity Simulator and will simplify device testing. The data gathered from the ADCs sampling the RF dri ve and RF reference is first demodulated using the non-IQ scheme [9]. The signals are then processed as a complex vector , allowing the model to operate in the baseband. One of the critical aspects of the firmware is the processing time. The expected delay introduced mostly by the cabling between the LLRF control system and the cavity is around 400 ns. The total processing time of the whole Cavity Simulator , including analog circuits and data con verters latency , shall match this value. The estimated latency introduced by the analog circuits and data con verters is around 250 ns. This means that the response of the model must be calculated in less than 18 clock c ycles. The primary function of the firmware is to simulate the behavior of the RF ca vity , high-power amplifier , and a con- nection between them through a circulator and a wav eguide. The block diagram presenting the model of those elements is shown in Fig. 6. A. Cavity Model The RF cavity is modeled as a parallel LCR circuit [10], which impedance can be expressed using the follo wing rela- tion: 5 Fig. 6. The block diagram presenting the simulation model. Z ( ω ) = 1 1 R L + 1 j ωL + j ω C = R L 1 − j R L ( 1 ω L − ω C ) (1) The L and C can be replaced with: L = R L Q L ω 0 (2) C = Q L ω 0 R L (3) where: Q L - is Q factor of the loaded Cavity and ω 0 is angular frequency of the cavity resonance. Z ( ω ) = R L 1 − j Q L ( ω 0 ω − ω ω 0 ) (4) The signals in the firmware will be operated in the baseband therefore it will be con venient to e xpress the ω as ω 0 + ∆ ω . Z (∆ ω ) = R L 1 − j Q L ( ω 0 ω 0 +∆ ω − ω 0 +∆ ω ω 0 ) = = R L 1 + j Q L ( ∆ ω ω 0 2 ω 0 +∆ ω ω 0 +∆ ω ) (5) Because in our aplication ω 0 ∆ ω the following assump- tion is possible: 2 ω 0 + ∆ ω ω 0 + ∆ ω ≈ 2 (6) Based on this we obtain: Z (∆ ω ) = R L 1 + 2 j Q L ∆ ω ω 0 (7) System with such transmission can be implemented as a dig- ital filter with sampling period T . The bilinear transformation is used to calculate it’ s parameters. j ∆ ω = 2( z − 1) T ( z + 1) (8) Z ( z ) = R L 1 + 4 Q L ( z − 1) ω 0 T ( z +1) = R L + R L z − 1 ( 4 Q L ω 0 T + 1) + (1 − 4 Q L ω 0 T ) z − 1 (9) These calculations assumed, that the cavity resonance matches precisely the reference signal frequency , b ut to sim- ulate the phenomena such as piezo compensation, or Lorentz force detuning a possibility to change the resonance frequency is required. For the digital filters operating on the complex signals, it can be realized by modifying the delay block of the firmware in the way sho wn in Fig. 7 [11]. T o calculate the trigonometric functions T aylor’ s theorem is used. It requires more resources than the typically used CORDIC algorithm but needs much fe wer clock cycles to obtain the result (for a 32-bit resolution it is 5 vs. 32). Fig. 7. Change of the digital filter structure allowing the detuning. The other π -modes are simulated using filters with identical structure (but different parameters) connected in parallel. The cavity probe signal is calculated as a sum of outputs of those filters. It is assumed that all modes will detune by the same value. The detuning of the cavity is a sum of 5 components: • Lorentz Force detuning - calculated as a square of the probe signal’ s magnitude multiplied by a constant coef- ficient. • Piezo compensation - a sum of data from two ADCs sampling the piezo signals. • Microphonics - signal generated from a look-up table. • Constant detuning. • Mode frequency - dif ferent value for each π -mode. The detuning signal is filtered by an IIR digital filter that represents the mechanical response of the cavity . The 6 exact transfer function of this filter will be based on the measurements performed on the real cavities. The beam current is calculated from the IQ samples of the RF reference signal multiplied by the data from a look-up table allo wing to simulate different beam profiles. The beam current signal is added to ca vity forward signal, which drives the cavity model. B. Amplifier Model The amplifier model is designed to simulate follo wing phenomena: • limited bandwidth, • gain compression, • power supply ripple. The limited bandwidth is simulated with the same filter as the one used for the ca vity model. The main dif ference is much lower Q-factor and no detuning. The transfer characteristic of the amplifier is stored in two lookup tables representing the gain and phase shift. These tables are addressed by the input’ s signal magnitude, which is estimated using ” α Max + β Min” algorithm [12]. The power supply ripple signal is generated as a predefined wa veform. Its impact on the output signal amplitude and phase can be e xpressed using follo wing relations [13], [14]: ∆ θ = 2 π L q 2 eV k m ∆ V k V k (10) ∆ V out V out = 5 4 ∆ V k V k (11) Where ∆ θ is the output phase change, L is the distance between the input and output cavities, e is electron charge, m is electron mass, V k is the cathode voltage, V out is the amplitude of the output signal. C. Cir culator Model The circulator is modeled as a fully linear element. It gener- ates the cavity forward, and the amplifier reflected signal. Both of those are calculated as a sum of the ca vity reflected and amplifier forw ard signals multiplied by a constant predefined two by two matrixes. I V . C A V I T Y S I M U L A T O R M E A S U R E M E N T S T o prove the proper operation of the Cavity Simulator a series of measurements was performed. The parameters of the simulations were not based on the measurements of the real cavities, because they are not yet av ailable. Instead the values that may e xpose possible problems were selected. All measurements were performed using 704.51 MHz ref- erence signal generated by the Cavity Simulator . The results are presented belo w . A. T ransmission The Cavity Simulator’ s transmission between the RF input and cavity probe output was measured using a vector network analyzer . The Q factor of the main mode was set to 700 000. Three measurements were performed: • one mode no detuning, • one mode with 10 kHz detuning, • 6 modes with 0, -0.5, -0.9, -1.5, -2.4, and -3 MHz offsets, all with dif ferent R and Q L settings. Fig. 8 and 9 present the results. Fig. 8. T ransmision of Cavity Simulator with 0 and 10 kHz detunning. Fig. 9. T ransmision of Cavity Simulator with multiple π -modes The loaded Q-f actor and maximum of the transmission don’t change when the detunning is applied. Negligible distortion at the reference frequency is visible in the detunned transmission. It is caused by the limited carrier suppression of the vector modulator circuit. It can be improved by calibration of the vector modulator’ s IQ offsets. B. Gr oup Delay As mentioned in the Section III the processing time is one of design’ s critical parameters. T o verify it a group delay of Cavity Simulator was measured. The simulation parameters were identical with the transmission measurement with one mode. Due to the low po wer of the signal at far from resonance frequencies, the results were disturbed, so smoothing of the results was applied. The results with and without smoothing are shown in Fig. 10. 7 Fig. 10. Cavity Simulator’ s group delay . The results at the frequencies close to the resonance are mostly dominated by the group delay of the cavity filter . Con versely , the values measured (after smoothing) at far from resonance frequencies indicate the processing time which is below the required 400 ns. C. Cavity F illing and Decay T o confirm the proper operation of the Cavity Simulator also in the time domain, the cavity filling and decay was measured. The Cavity Simulator’ s output was driven with RF signal generated by the 7th RF output channel. The signal was turned on and off with 2 s period. The cavity filling and decay were recorded using fast digital oscilloscope. The results are presented in Fig. 11 and 12. The settings were identical to those used in the transmission measurement. Fig. 11. The input and output signals during cavity filling. The filling and decay times are approximately equal to 0.65 ms, which is within the expected range. No distortions of the signals were observ ed. V . C O N C L U S I O N In this paper , the hardware design, firmware, and measure- ments of the Cavity Simulator designed for European Spal- lation Source are described. Four units were manufactured, and the firmware with the main functionality was prepared. The measurements results confirm the proper operation of the device. Fig. 12. The input and output signals during cavity decay . The Ca vity Simulator is being further developed to extend its functionality and scope of the simulation. Ne xt tests, including those with LLRF control System, are also planned. A C K N O W L E D G M E N T W ork supported by Polish Ministry of Science and Higher Education, decision number DIR/WK/2016/03. R E F E R E N C E S [1] M. Eshraqi et al., The ESS Linac , IP AC 2014, Dresden, Germany , 2014. [2] A. J. Johansson, A. Svensson, F . Kristensen and R. Zeng, LLRF System for the ESS Proton Accelerator , IP AC 2014 Dresden, Germany , 2014. [3] J. Szewi ´ nski et al., Contrib ution to the ESS LLRF System by P olish Electr onics Group , IP AC 2017, Copenhagen, Denmark, 2017. [4] G. Dev anz et al., ESS Eliptical Cavities and Cryomodules , SRF 2013, Paris, France, 2013. [5] T . Czarski, K. T . Pozniak, R. S. Romaniuk, and S. Simrock, TESLA cav- ity modeling and digital implementation in FPGA technology for contr ol system development , Nuclear Instruments and Methods in Physics Re- search Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, V olume: 548, 2005. [6] C. Serrano, L. Doolittle and V . K. Vytla, Cryomodule-On-Chip Simula- tion Engine , ICALEPCS 2017, Barcelona, Spain, 2017. [7] F . Qiu et al., Real-time cavity simulator-based low-level radio-frequency test bench and applications for accelerators , Physical Revie w Acceler- ators and Beams, V olume: 21, Issue: 3, 2018. [8] I. Rutkowski, K. Czuba and M. Grzegrz ´ ołka, LO Board F or 704.42 MHz Cavity Simulator F or ESS , ICALEPCS 2017, Barcelona, Spain, 2017. [9] L. Doolittle, H. Ma and M. S. Champion, Digital Low-Level RF Control Using Non-IQ Ssampling LINA C 2006, T ennessee, USA, 2006. [10] T . Schilcher, V ector Sum Control of Pulsed Accelerating Fields in Lor entz F orce Detuned Superconducting Cavities , Ph.D. thesis, Univer - sit ¨ at Hambur g, 1998. [11] K. W . Martin, Complex Signal Pr ocessing Is Not Complex , IEEE T ransactions on Circuits and Systems I: Regular Papers, V olume: 51, Issue: 9, 2004. [12] Richard G. L yons, Understanding Digital Signal Pr ocessing , Prentice Hall PTR, 2004. [13] M. Hara, T . Nakamura and T . Ohshima, A Ripple Effect Of a Klystron P ower Supply On Synchr otr on Oscillation , Particle Accelerators, V ol- ume: 59, 1998. [14] R. Zeng, D. McGinnis, S. Molloy and A. J. Johansson, Influence of the Dr oop and Ripple of Modulator on Klystron Output , IP AC2012, New Orleans, Louisiana, USA, 2012.

Original Paper

Loading high-quality paper...

Comments & Academic Discussion

Loading comments...

Leave a Comment