ESS 캐비티 시뮬레이터: 실시간 LLRF 테스트를 위한 고성능 FPGA 기반 솔루션

본 논문은 유럽 스팔레이션 소스(ESS) 가속기용 초전도 캐비티를 실제 장치 없이 검증할 수 있도록 설계된 Cavity Simulator를 소개한다. 704.42 MHz 동작 주파수와 피에조 보상, 비틀림, 마이크로폰닉스, 증폭기 비선형성 등을 FPGA 기반 디지털 모델로 구현하고, 벡터 모듈레이터와 고속 ADC/DAC를 이용해 실시간 RF 신호를 생성한다. 하드웨어와 펌웨어 설계, 지연 최소화 기법, 그리고 측정 결과가 상세히 제시된다.

저자: Maciej Grzegrzo{l}ka, Krzysztof Czuba, Mateusz Lipinski

본 논문은 유럽 스팔레이션 소스(ESS) 가속기의 중·고베타 섹션에 사용되는 704.42 MHz 초전도 캐비티를 실제 장치 없이 검증하기 위한 Cavity Simulator의 설계와 구현을 상세히 기술한다. ESS는 120여 개의 초전도 캐비티를 갖추게 되며, 각각은 독립적인 LLRF(저전력 라디오 주파수) 제어 시스템에 의해 제어된다. 실제 캐비티와 고전력 RF 증폭기를 사용해 테스트하면 장비 손상 위험이 크므로, 폴란드 전자 그룹(PEG)과 룬드 대학교가 공동으로 개발한 시뮬레이터가 필요하게 되었다.

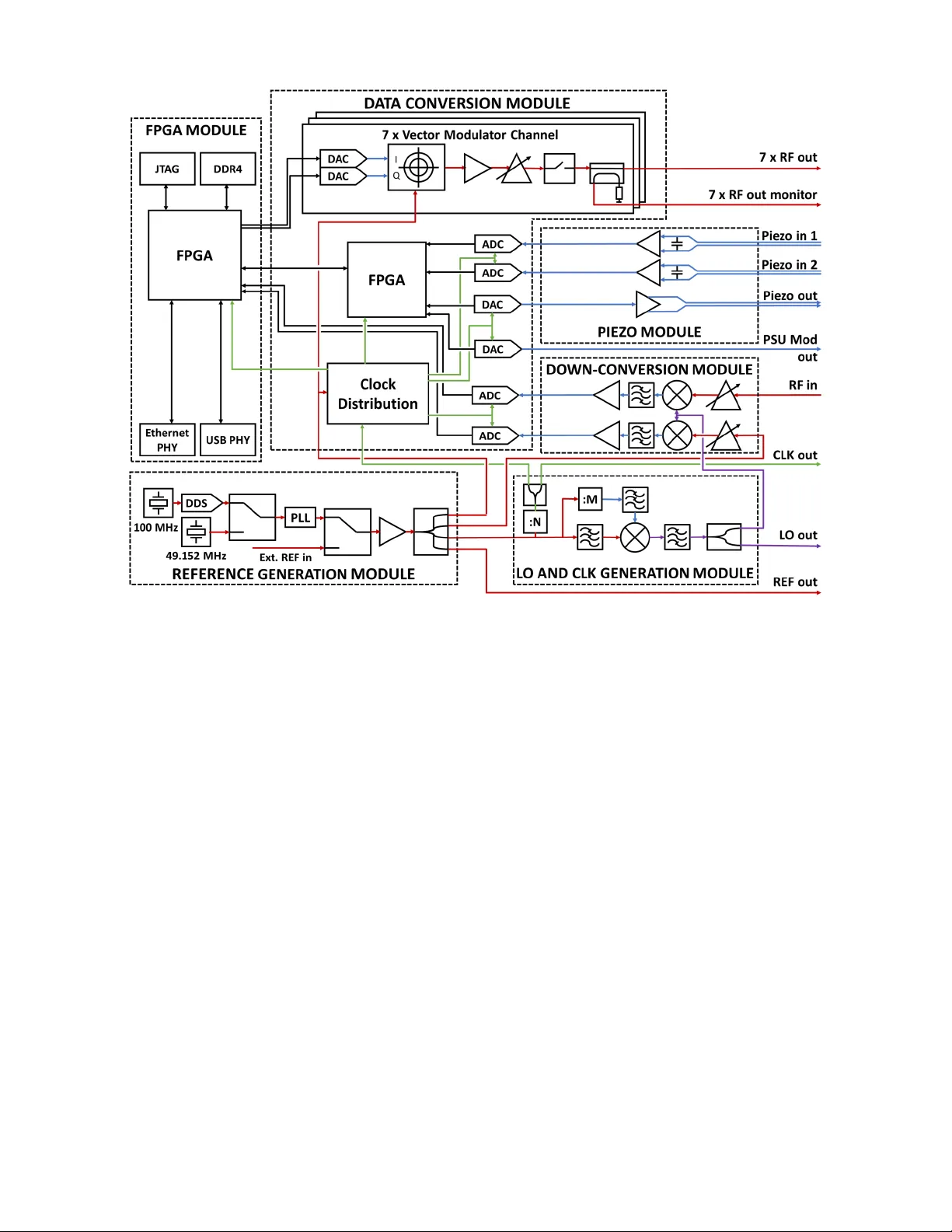

시뮬레이터는 크게 하드웨어와 펌웨어 두 부분으로 나뉜다. 하드웨어는 19인치 랙에 탑재되는 7개의 모듈로 구성된다. 핵심 FPGA 모듈은 Xilinx KCU105 보드이며, USB·이더넷 PHY를 내장하고 있어 외부와의 통신을 담당한다. 데이터 변환 모듈은 250 MSPS 16‑bit ADC 두 개와 5 MSPS 18‑bit ADC 두 개를 포함해 RF 드라이브·레퍼런스와 피에조 신호를 샘플링한다. 또한 8개의 DAC를 통해 6개의 RF 출력, 피에조 센서, 전원 모듈 신호를 생성한다. RF 신호는 벡터 모듈레이터 회로와 결합된 DAC를 사용해 정확한 I/Q 균형을 유지한다. 다운컨버전 모듈은 두 개의 액티브 믹서를 이용해 RF를 IF로 변환하고, LO·클럭 모듈은 117.4 MHz 클럭과 729.58 MHz·736.44 MHz LO를 직접 아날로그 합성 방식으로 제공한다. 레퍼런스 생성 모듈은 PLL‑VCO 회로로 704.42 MHz를 생성하며, 크리스털 기반·DDS 기반 두 가지 경로를 지원한다. 전원 공급 모듈은 +12 V를 제공하고 전원 순서를 관리하며, 팬 속도와 전류를 모니터링한다.

펌웨어는 두 개의 FPGA 중 데이터 변환 모듈에 탑재된 저성능 FPGA와 메인 FPGA(Processing Module)로 구분된다. 메인 FPGA는 MicroBlaze 소프트웨어 코어를 이용해 이더넷·USB 통신, 파라미터 설정, DDR4 메모리 관리 등을 수행한다. 핵심 DSP 로직은 ADC에서 획득한 RF 신호를 비‑IQ 방식으로 디모듈레이션하고, 복소수 벡터 형태로 변환해 베이스밴드에서 처리한다.

캐비티 모델은 병렬 LCR 회로를 디지털 필터(바이리니어 변환)로 구현한다. 기본 전송 임피던스 Z(Δω)=R_L/(1+2jQ_LΔω/ω₀) 형태를 Z‑변환하여 z‑도메인 필터 계수를 도출한다. 주파수 편이 Δω는 디지털 지연 블록을 변형해 실시간으로 조정한다. 다중 π‑모드(6개)는 동일 구조의 필터를 병렬 연결해 각각 다른 R·Q값을 부여한다. 비틀림(Detuning)은 Lorentz 힘(프로브 전압 제곱·상수), 피에조 보상(두 ADC 입력), 마이크로폰닉스(룩업 테이블), 상수 비틀림, 모드별 고유 주파수 오프셋을 합산해 계산한다. 이 합성 비틀림 신호는 기계 응답을 모사하는 IIR 필터를 통과한다.

증폭기 모델은 제한된 대역폭, 이득 압축, 전원 리플을 재현한다. 대역폭은 캐비티와 동일한 구조의 저 Q‑값 필터로 구현하고, 이득·위상 특성은 입력 신호 크기에 따라 LUT에서 조회한다. 입력 크기 추정은 “α·Max + β·Min” 알고리즘을 사용한다. 전원 리플은 사전 정의된 파형으로 생성하고, 위상·진폭 변화를 식(10)·(11)로 적용한다.

순환기 모델은 선형 2×2 매트릭스로 구현해 캐비티 전방·반사와 증폭기 전방·반사 신호를 결합한다.

지연 요구사항은 전체 시스템이 400 ns 이내에 응답해야 하므로, 아날로그·컨버터 지연(≈250 ns)을 제외한 FPGA 내부 연산은 18 클럭 사이클 이하로 처리하도록 설계되었다. 이를 위해 삼각함수 계산에 CORDIC 대신 테일러 전개를 사용해 32‑bit 정밀도에서 5 사이클만에 결과를 얻는다.

측정 결과는 다음과 같다. 전송 특성은 VNA를 이용해 0 kHz와 10 kHz 비틀림 상황에서 Q‑factor 7 × 10⁵를 유지했으며, 다중 π‑모드 테스트에서도 각 모드별 설정값이 정확히 재현되었다. 그룹 지연 측정에서는 설계 목표인 400 ns 이하가 확인되었으며, 고주파 스퍼는 외부 측정 장비와 DC‑DC 컨버터에서 발생한 것으로 파악되었다.

결론적으로, 이 Cavity Simulator는 실제 초전도 캐비티와 거의 동일한 전기·기계 동작을 실시간으로 제공함으로써 LLRF 제어 알고리즘 개발, 하드웨어 검증, 시스템 통합 테스트를 안전하고 효율적으로 수행할 수 있게 한다. 향후 실제 캐비티 측정값을 반영해 파라미터를 보정하면 더욱 정밀한 시뮬레이션이 가능할 것으로 기대된다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기