Logic circuits from zero forcing

We design logic circuits based on the notion of zero forcing on graphs; each gate of the circuits is a gadget in which zero forcing is performed. We show that such circuits can evaluate every monotone Boolean function. By using two vertices to encode…

Authors: Daniel Burgarth, Vittorio Giovannetti, Leslie Hogben

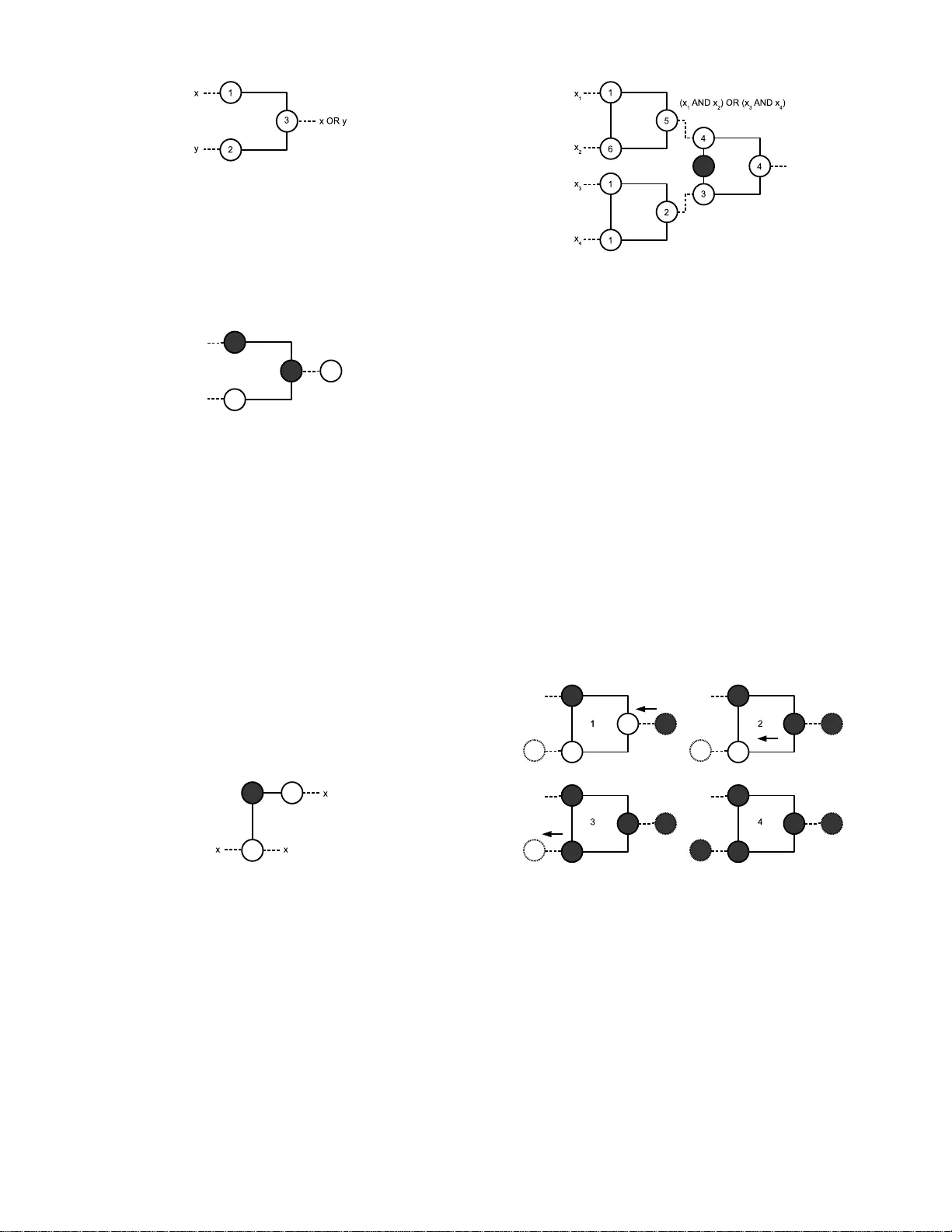

Logic circuits from zero for cing Daniel Burgar th ∗ Institute of Mathematics and Physics, Ab erystwyt h University, SY23 3BZ Ab erystwy th, Unite d Ki ngdom Vittorio Giov annetti † NEST, Scuola Normale Sup erior e and Istituto Nanos cienze-CNR, Piazza dei Cavalieri 7, I-5612 6 Pisa, Italy Leslie Hog be n ‡ Dep artment of Mathematics, Iowa St ate University, Ames, IA 50011, USA, and Americ an Institute of Mathematics, 3 60 Portage A ve, Palo Alto, CA 94306, USA Simone Severini § Dep artment of Computer Scienc e, and Dep artment of Physics & Astr onomy, University Col le ge L ondon, WC1E 6BT L ondon, Unite d Ki ngdom Michael Y oung ¶ Dep artment of Mathematics, Iowa St ate Univers ity, Ames, IA 50011, USA W e design logic circuits b ased on the n otion of zero forcing on graphs; each gate of the circuits is a gadget in which zero forcing is p erformed. W e show that suc h circuits can ev aluate every monotone Boolean function. By using t w o v ertices to enco de eac h logical b it, we obtain univ ersal computation. W e also highlight a phenomenon of “back forcing” as a prop erty of each function. Such a phenomenon o ccurs in a circuit when the input of gates whic h ha ve b een a lready used at a giv en time step is further modified by a computation actually performed at a later stage. Finally , we sho w that zero forcing can b e also used to implemen t rev ersible compu t ation. The model introdu ced here p ro vides a potentially new tool in t h e an alysis of Bo olean functions, with particular atten t ion to monotonicity . I. INTRO DUCTION W e order the tw o elements of a set Σ = { 0 , 1 } such that 0 < 1. This extends to a partial ordering on the set Σ n = { 0 , 1 } n by comparing words co ordinate-wise . Let x = x 1 ...x n and y = y 1 ...y n . Here, x y means that x i ≥ y i , for every i = 1 , ..., n . A Bo ole an function f : Σ n − → Σ is monotone when f ( x ) ≥ f ( y ) if x y , for ev ery x, y ∈ Σ n . Monotone Bo o lean functions hav e an impo r tant ro le for pro ving lo wer b ounds of circuit complexit y (see, e.g. , Leeuw en [9], Chapter 14.4). An y f unction obtained by compo sition of mo notone Bo o lean functions is itself monotone. Examples of monotone Bo o lean functions are the c onjuction AND and the disjunction OR . Indeed, ev- ery monotone Bo o lean function can be rea liz ed by AND and OR op era tio ns (but without NOT ) . Bo olea n functions are important in applications, for e xample, in the im- plement ation of a class of no n- linear digital filters called stack filters [4 ]. Imp or tant metho ds for obtaining non- trivial bounds on specific monotone Boole an functions hav e been studied (see, e.g. , [2]). ∗ Electronic address: daniel@burgarth.de † Electronic address: v.gio v annetti@sns.it ‡ Electronic address: lhogben@iastate.edu; hogb en@aimath.org § Electronic address: simosev e@gmail.com ¶ Electronic address: m young@iastat e.edu The concept of zer o for cing on graphs is a recent idea that is part of a program studying minim um ranks o f matrices with sp ecific combinatorial constraint s. Zero forcing has b een also ca lled graph infection and g raph propaga tion [6, 10]. Notice that, in the co nt ext describ ed here, the ter m “zero forcing” s eems to be unfortunate, bec ause w e are forcing ones , not ze r os. How ever, we keep the ter m giv en that this is now the most commonly used in the literature. In order to define zero forcing , w e first need to define a c olor-change rule : if G = ( V , E ) is a graph with each vertex colo red either white o r black, u is a black vertex of G , and exactly one neig hbor v of u is white, then c hange the color o f v to black. Given a coloring of G , the final c oloring is the r e s ult of applying the co lor-change rule un til no more changes are p ossible. A zer o for cing set for G is a set Z ⊆ V ( G ) such that if the element s of Z a r e initially colored black and the elements of V ( G ) \ Z ar e colored white, the final colo ring of G is all bla ck. Zero forcing is related to certa in minim um rank/max imu m nullit y pro blems of matrices asso ci- ated to gra phs (see [3]) and to the controllabilit y of quantum spin systems [5 , 6]. Minimimizing the size of zero f orcing sets is a difficult co mbinatorial optimizatio n problem [1]. The remainder of this pa p er is organized as follo ws. In Section 2, w e prov e that ze r o forcing o n graphs rea liz es all monotone Boo lean functions, and highlight some sim- ple related facts. The connection b e t ween zero for cing and circuits is o btained by asso ciating a gra ph to each 2 logic gate. W e will show that the functions AND and OR are indeed easily r ealized by tw o different ga dg ets with a few vertices. This is not the firs t work obser ving that monotone Bo olean functions can b e rea lized in a com bi- natorial setting. F o r example, Demaine et al. [7] have used the mo vements of a collections of simple in terlo cked po lygons. In Section 3 , w e describ e the phenomenon o f b ack fo r c- ing in the circuit. The phenomenon o ccur s when the color-change rule acts to mo dify the color of a vertex which has been already used during the computation. In some ca ses, back forcing implies that information ab out the output of a Bo o lean circuit can b e read not just by lo oking a t the color of a tar get vertex corre sp onding to the final output of the pro ces s , but at the color of the vertices in cer tain intermediate or initial gadg ets. The idea op ens a simple but intriguing scenario consisting of many par ties that perfor m computation in a distributed wa y: ea ch pa rty holds a subset of the gates and it is able to read certain information ab out the input of other pa r- ties, s ince the co lor of its gates may hav e been mo dified by back forcing. Back forcing can b e avoided b y including some extra gadget acting as a filter. In Section 4, we show that zero for c ing b eco mes u niver- sal , i.e. , it can rea lize an y Bo olean function, if w e apply a prop er encoding. Sp ecifically the dual r ail enc o ding , where tw o vertices are as signed to ea ch lo gical bit, is a metho d to co nstruct the NOT gate and therefore to obtain universal computatio n. Conclusions are in Section 5. II. MAIN RESUL T Our main result is easy to prove: Theorem 1 Zer o for cing r e alizes al l monotone Bo ole an functions. Pro of. It is sufficient to show that zero forcing r ealizes the functions AND and OR . Claim 1. The gate AND is realized by the gadget G AND with vertices { 1 , 2 , 3 } and e dges {{ 1 , 2 } , { 1 , 3 } , { 2 , 3 }} , where 1 and 2 ar e th e input v ertices and 3 is the output vertex, co ntaining the res ult and being a ble to propagate the c o lor. All vertices are initially colo red white. An illustration of the gadget G AND is be low: FIG. 1: The gate for the function AND . Pr o of of Claim 1. If no a ction is taken then the fina l coloring of the gadge t is white. If w e color vertex 1 black then the final colo ring is all white but for vertex 1. The same holds for v ertex 2. How e ver, if we colo r vertex 1 and vertex 2 black then the color -change rule implies that vertex 3 is blac k a t step 2 . In fact, { 1 , 2 } is a zer o forcing set for G AND . Claim 2. The gate OR is rea liz ed b y the gadget G OR with vertices { 1 , 2 , 3 , 4 } and edges {{ 1 , 3 } , { 1 , 4 } , { 2 , 3 } , { 2 , 4 }} , where 1 and 2 ar e the in- put vertices. The output vertex is vertex 4. V ertex 3 is initially colored black: FIG. 2: The gate for the function OR . Pr o of of Claim 2. If no action is taken then the final coloring of the g a dget is all white, but for vertex 3. If we color vertex 1 black then the color - change rule implies that vertex 4 is black at step 2. The same holds for vertex 2 and for v ertex 1 and vertex 2 to gether. In f act, { 1 , 3 } , { 2 , 3 } , { 1 , 2 , 3 } are zero forcing s ets for G OR , a ble to pr opaga te the color for inducing the nex t s tep o f the computation. It is imp ortant to observe that zer o forcing do es not realize the function NOT , since when a vertex is colored black, it can not c hange colo r anymore. The consequence is that z e r o forcing do es not realize universal computatio n (any B o olean function can b e implemented us ing AND , OR and NOT gates) but monotone Boolea n functions only . This concludes the proof. It may b e worth obs e r ving the follo wing p oints: • Notice that extra vertices forming delay lines may be needed to assemble a circuit such that the out- put produced by zero forcing in par allel gates is syncronous . How ever, given our choice of ga dgets, exactly 2 tim e s teps ar e requir ed for o utput of zero forcing in G AND and G OR . At time step 3 the color- change rule acts o n the next gate in the circuit. There is then a convenien t distinction b etw een in- ternal and external time: internal time refers to the zero forcing steps ins ide the gadgets/ gates; extern al time refers to the time steps of the computation. • The g adgets G AND and G OR hav e three and four vertices, res p ectively . B y insp ection on a ll po ssible combinations of white and blac k vertices for graphs with at most four v ertices , w e can observe that we hav e chosen the smallest p ossible gadgets, in terms of num b er of vertices a nd edges, realizing the tw o functions. O ne migh t think that the gate OR is realized also by the ga gdet with three vertices in the figure: Although the gadget implements the OR co rrectly , it cannot b e used a s an initial o r intermediate gate 3 FIG. 3: A gate for the function OR , where color-c hange rule does not mov e the inp ut forward. of a circuit, since in this gadget the color-change rule does not mov e fo w ards the o utput to the next gate, but it halts a t vertex 3: FIG. 4: The figure shows that an OR gate in w hich all vertices are initially white do es not mov e t he inpu t forw ard. • Let us consider the gadg et G OR . If w e colo r ver- tex 1 blac k then the color-change rule implies that vertex 4 is black at step 2. Suppos e tha t vertex 2 is color e d white at step 1. At step 2 the gate has computed the OR function in v ertex 4 with input { 0 , 1 } . At step 2 vertex 2 is als o colored black un- der the action of the color-change rule, b ecause this is the unique white neig hbo ur of vertex 3. This is necessary in or de r for the computation to pr o ceed using the output (black vertex 4). So, for a ll inputs with output 1 , the vertices of G OR are bla ck after t wo steps of the internal time. Suc h b e haviour is discussed in more detail in t he next section. • It is straigh tforward to realize the op eratio n COPY : FIG. 5: The gate for the function COPY . II I. BACK F OR CING If eac h B o olean v ar iable in the input of a circuit is set to 1, then the v er tices of the circuit that are initially colored bla ck for m a zero forc ing set. How ever, this is not the only situation in which we hav e a ze r o forcing set. The next figure giv es an example: This is a cir cuit computing the Bo olea n function ( x 1 AND x 2 ) OR ( x 3 AND x 4 ). The num b er in the vertices o f FIG. 6: A circuit computing the Boolean fun ction ( x 1 AND x 2 ) OR ( x 3 AND x 4 ). The circuit exhibits the phen omenon of back forcing. the figure specify the internal time step at whic h the v er- tex is blac k; the vertices la b eled by 1 are initially colored black. The output of the circuit is 1 at step 4 and at step 6 of the internal time the vertices enco ding the input of the function are all color ed black. This c a n happ en if and only if thr e e o f the input vertices a r e colored white at in ter nal time 1. The phenomenon will b e ca lle d b ack for cing , b e cause it is induced b y the color- change r ule acting backwards with resp ect to the direction fro m input to output in the whole circuit. The gadg e t G AND exhibits back forcing conditionally on having input { 0 , 1 } . The t yp e of back forcing in G AND can b e called tra nsmittal b ack for cing , bec ause if s o mething back forces its output black then the gate transmits the bac k fo rce, i.e. , it mo difies the color of the output vertex in a g ate used pre viously . The figure clarifies the dynamics: FIG. 7: The steps of bac k forcing. The gadget G OR needs to force an input forw a rd in order to color black o ne of the output vertices adjacent to its inputs and in another gate. In this sense , G OR do es not ha v e tr ansmittal back forcing . In other w o r ds, a gate at external time t , can no t back force its color in to G OR at exter nal time t + 1. In contrast, the circuit ( x 1 AND x 2 ) OR ( x 3 AND x 4 ) can initiate bac k for cing as de s crib ed ab ov e (when it an in termediate element in the cir cuit). W e can also slow do wn back forcing, by including ap- propriate delay lines – f or ex ample, by adding extra ver- tices in each gadget o r b etw een them. Alternatively , we 4 could consider dela y lines directly embedded in the struc- ture of the gadgets implemen ting the logical gates. Also, back for cing can b e a voided completely by in- cluding th e gadget b elow. The gadg e t acts as a filter . In some sense, the filter c a n be understo o d as an ele ctr onic dio de allowing ze r o forcing only in o ne direction: FIG. 8: A gadget acting as a filter: its role is to av oid bac k forcing. In relatio n to the circuit for the function ( x 1 AND x 2 ) OR ( x 3 AND x 4 ), it ma y b e in teresting to see that if there are tw o parties each one chosing the input of one of the t wo AND gates , and ea ch one having acc ess to only the corrisp o nding vertices, given the back forcing, the parties can then learn the output o f the c ir cuit by lo oking at the co lor o f their vertices at the end o f the computation, except when a party chooses (0 , 0) ( i.e. , white, white). IV. UNIVERSALITY Despite the fact that the co lo r-change rule induces a non-reversible process (black coloring cannot be undone) a simple mo dification of the enco ding stra tegy allows us to implement universal, and hence also re versible, co m- putation. The idea is to adopt a dual r ail stra tegy , where tw o ver- tices are employ ed to enco de a single lo gic al bit . Specifi- cally , as shown in Fig. 9, in this sc heme w e a sso ciate the logical bit 0 to a co nfiguration in which (say) the first ver- tex is colored in black while the second is kept white, and the logical 1 to the opp osite configuratio n (i.e. the first vertex being left white and the second one being color e d black). With such enco ding w e can now design the ga te NOT by simply dr awing a graph in whic h the nodes a re exchanged at the output (see Fig. 10). A lso a dual rail AND gate can b e e asily realized. Universal c o mputation is hence achieved by constructing a NAND ga te via conc a te- nation of AND with NOT and by observ ing that the COPY gate for the dua l rail enco ding is simply obtained by just applying to both the no des that form a bit the transfor- mation of Fig. 5. Once universal computation has b een achiev ed, w e can easily turn it into a r eversible one, e.g. , by building a T offoli gate [12]. This to remar k that even if zero forcing is a n irreversible pro ce s s, it ca n still b e used to induce a rev e r sible computational dynamics. FIG. 9: Ph y sical bits for 0 and 1 in a dual rail encoding. FIG. 10: In a dual rail enco ding the logical NOT can be im- plemented by sw apping the physical bits. V. CONCLUSIONS W e hav e shown that all monotone Bo olea n functions can be realized b y zero forcing in a gr aph constructed by gluing toge ther the co pies of t wo t ype s of sub- graphs/ g adgets cor resp onding to the Bo o lean gates AND and OR . W e ha ve briefly discus sed the minimalit y of such gadgets in terms of v er tices and edges. W e hav e highlighted a ba ck forcing action. Back for c - ing has an effect on the co lo ring of gates alr eady us ed, as a function of what has happened in the “future”, i.e. , at a later stag e o f the co mputation. Because of the rela- tion b etw een zer o forcing and minim um ranks, the mo del describ ed here is amenable to b e s tudied with linear al- gebraic to o ls , p otentially sug g esting a no vel direction in the analysis of monotone B o olean functions. Finally , we ha ve shown that univ ersal computations can b e obtained b y zero forcing by simply adopting a dual rail encoding. An op en pro blem sugg ested by the pap e r is to under- stand the link b etw een zero forcing a nd the dynamics a t the bas is of o ther unconv entional mo dels of computation, like, fo r example, the billiard ball computer – in tro duced as a model o f rev ersible computing [8] –, mode ls involving geometric ob jects, and dominos [7]. Ackno wle dgments This work has b een do ne while DB w as with the Black- ett La b orator y at Imp erial College London, supp orted by E PSRC grant EP /F043 678/1 . VG ac knowledges sup- po rt by the FIRB-IDEAS pro ject (RBID08 B 3FM). SS is a Newton In ter national F ello w. 5 [1] A. A azami, Har dness r esults and appr oximation algo- rithms for some pr oblems on gr aphs , Ph.D . thesis, Un i- versi ty of W aterlo o, Dec. 2008. [2] N. Alon, R. Boppana, The mon otone circuit complexity of Bo olean functions, Combinatoric a , 7 , (1986), 1-22. [3] American I nstitute of Mathematics (AIM) Minim um Rank-Sp ecial Graphs W ork Group, AIM Minim um R an k – Sp ecial Graphs W ork Group (F. Barioli, W. Barrett, S. Butler, S. M. Cioab˘ a, D . Cvetk o vi´ c, S. M. F allat, C. Go d- sil, W. Haemers, L. Hogben , R. Mikkelson, S. Nara ya n, O. Pryp orov a, I. Sciriha, W. So, D. S tev anovi ´ c, H. v an der Holst, K. V ander Meulen, A. W angsness), Zero forc- ing sets and th e minimum rank of graphs, Line ar Algebr a and Its Applic ation 428 (20 08), 1628-1648. [4] J. A stola, D. Ako pian, O. V ainio, and S. A gaian, New digit-serial implementation of stac k filters, Di scr ete Ap- plie d Mathematics , 61 , pp. 181–197, 1997 . [5] D. Burgarth, S. Bose, C. Bruder, V. Gio v annetti, Lo cal contro llabilit y of qu antum net w orks, Phys. R ev. A 79 , 060305(R) (2009). [6] D. Burgarth and V. Gio vannetti, F ull control b y lo cally induced relaxation, Phys. R ev. L ett. 99 , 100501 ( 2007). [7] E. D. Demaine, M. L. Demaine, R. Uehara, A ny mono- tone b o olean function can b e realized by interlock ed p oly- gons, C CCG 2010 , 139-142. [8] E. F red kin and T. T offoli, Conserv ative logic, Interna- tional Journal of The or etic al Physics , vol. 21, no. 3, pp. 219–253 , 1982. [9] J. Leeu w en , Handb o ok of The or etic al C omputer Scienc e , Elsevier S cience Pub lishers, 1990. [10] S . Sev erini, N ondiscriminatory Propagation o n T rees, J. Phys. A: Math. The or. 41 482002, 200 8. [11] P . Vitanyi, Time, S pace, and Energy in Rev ersible Com- puting, Pr o c. 2005 ACM Internat ional Confer enc e on Computing F r ontiers , Ischia, Italy , 4-6 May 200 5, 1st In - ternational W orkshop on Rev ersible Computing. [12] T. T offoli, Reversible comput ing, T e chnic al R ep ort MIT/LCS/TM-151 , 198 0.

Original Paper

Loading high-quality paper...

Comments & Academic Discussion

Loading comments...

Leave a Comment