제로 포싱으로 구현하는 논리 회로와 보편 연산

이 논문은 그래프의 제로 포싱 규칙을 이용해 AND·OR 게이트를 구현하고, 두 정점으로 논리 비트를 인코딩함으로써 모든 부울 함수를 구현할 수 있음을 보인다. 또한 “백 포싱” 현상을 정의하고, 이를 제어하는 필터와 지연선 기법을 제시한다. 듀얼 레일 인코딩을 통해 NOT 게이트를 만들고, 결과적으로 가역 및 비가역 보편 계산이 가능함을 증명한다.

저자: Daniel Burgarth, Vittorio Giovannetti, Leslie Hogben

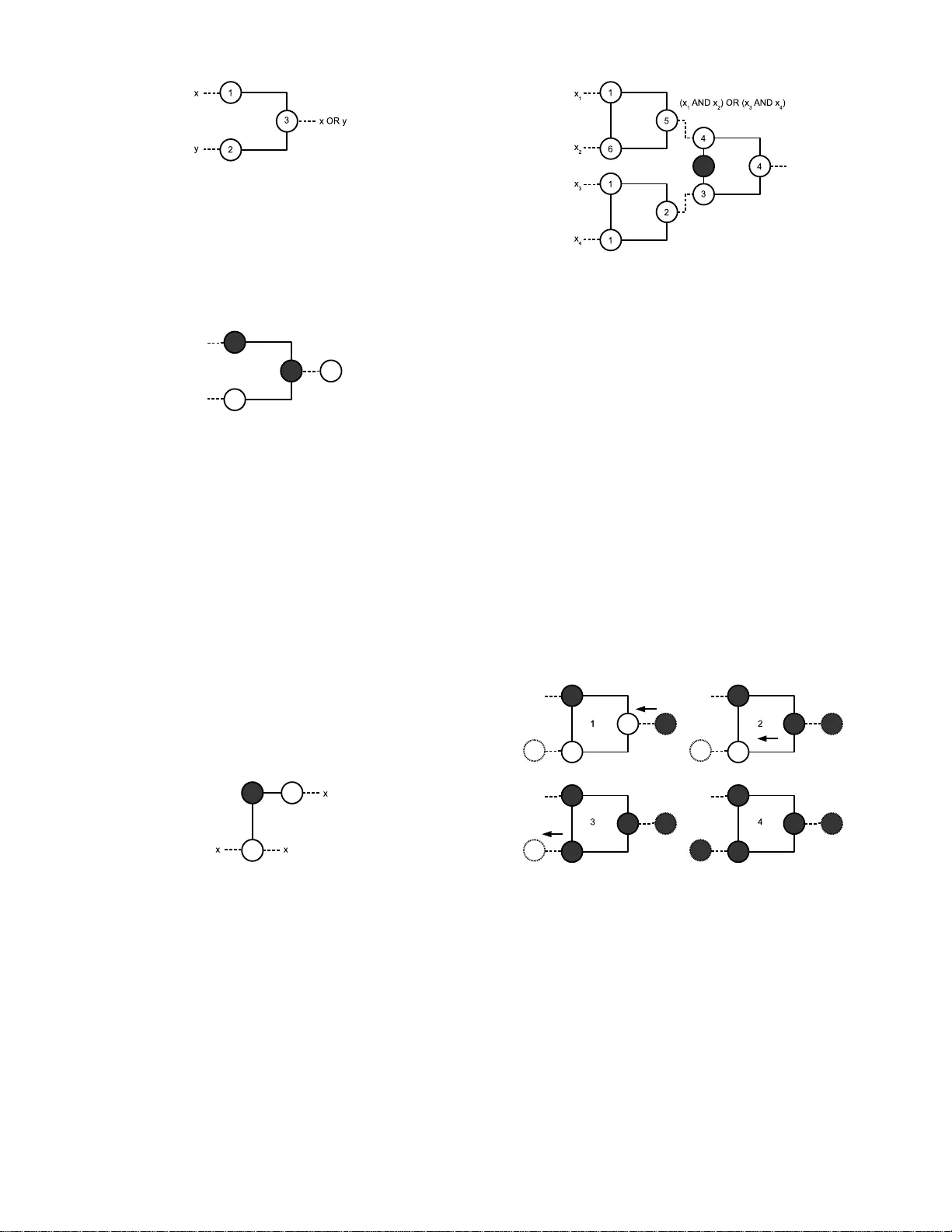

논문은 먼저 부울 함수의 단조성 개념을 소개하고, 단조 함수가 AND·OR 연산만으로 구성될 수 있음을 상기한다. 제로 포싱의 정의를 제시하면서, 흰색 정점이 검은색으로 변하는 ‘색 변화 규칙’과, 전체 그래프가 검은색이 되도록 하는 최소 시작 집합을 ‘제로 포싱 집합’이라 부른다. 이후 주요 결과인 정리 1을 제시한다. 정리 1은 제로 포싱을 이용하면 모든 단조 부울 함수를 구현할 수 있음을 주장한다. 이를 증명하기 위해 두 기본 게이트를 설계한다.

첫 번째 게이트는 AND 게이트이다. 정점 1·2를 입력, 정점 3을 출력으로 하는 완전 그래프 K₃를 사용한다. 초기 상태에서 입력 정점이 모두 검은색이면, 정점 3이 유일한 흰 이웃을 갖게 되어 두 번째 단계에서 검은색으로 변한다. 하나만 검은색이면 출력은 변하지 않는다. 두 번째 게이트는 OR 게이트이다. 정점 1·2를 입력, 정점 4를 출력으로 하고, 정점 3을 중간 검은색 정점으로 둔 네 정점 그래프를 사용한다. 입력 중 하나가 검은색이면 정점 4가 두 단계 안에 검은색이 된다. 두 게이트 모두 최소 정점·간선 수를 갖는 최적 구조임을 논문은 검증한다.

그 다음 ‘백 포싱(back forcing)’ 현상을 정의한다. 회로가 진행되는 동안, 뒤쪽 단계에서 발생한 색 변화가 앞쪽에 이미 사용된 입력 정점의 색을 다시 바꾸는 현상이다. 예시로 (x₁∧x₂)∨(x₃∧x₄) 회로를 제시하고, 특정 입력 조합에서 출력이 1이 된 뒤 내부 시간 6에서 입력 정점까지 검은색이 전파되는 과정을 설명한다. 백 포싱은 두 종류로 구분한다. ‘전송 백 포싱(transmittal back forcing)’은 AND 게이트에서 발생하며, 출력이 뒤에서 강제되면 입력도 바뀐다. OR 게이트는 이러한 전송을 갖지 않는다. 백 포싱은 정보가 회로 외부에서 내부로 역전파될 수 있음을 보여 주며, 다자간 분산 계산 시 다른 참여자가 자신의 입력을 통해 전체 출력 여부를 추론할 수 있게 만든다. 이를 방지하기 위해 필터 게이트와 지연선(추가 정점)을 삽입하는 방법을 제시한다. 필터는 색 변화가 한 방향으로만 흐르도록 설계된 작은 그래프이며, 지연선은 내부 시간 차이를 조절해 동기화를 맞춘다.

다음으로 보편 계산을 위한 ‘듀얼 레일 인코딩’ 방식을 소개한다. 하나의 논리 비트를 두 정점에 매핑하고, (검·흰)과 (흰·검) 두 배치를 0과 1에 대응시킨다. 이 인코딩을 사용하면 NOT 게이트를 단순히 두 정점의 위치를 교환하는 그래프로 구현할 수 있다. 듀얼 레일 AND와 NOT을 조합하면 NAND 게이트를 만들 수 있고, NAND는 모든 부울 함수를 구현하는 완전 집합이므로 보편 계산이 가능해진다. 또한, 이러한 구조는 가역 계산을 위한 토플리 게이트 등으로 확장될 수 있다. 비록 제로 포싱 자체는 비가역적이지만, 듀얼 레일 인코딩을 통해 전체 회로를 가역적으로 설계할 수 있음을 강조한다.

마지막으로, 제로 포싱이 최소 행렬 랭크와 연결된다는 점을 언급하며, 선형 대수적 도구를 이용해 단조 부울 함수의 복잡도와 회로 최적화를 연구할 새로운 방향을 제시한다. 논문은 또한 물리적 구현(양자 스핀 네트워크, 광학 회로 등)과의 연계 가능성을 제시하며, 향후 연구 과제로 빌리어드 볼 컴퓨터, 도미노 기반 모델 등과의 관계를 탐구할 것을 제안한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기