Thermal analysis is increasingly critical in modern integrated circuits, where non-uniform power dissipation and high transistor densities can cause rapid temperature spikes and reliability concerns. Traditional methods, such as FEM-based simulations offer high accuracy but computationally prohibitive for early-stage design, often requiring multiple iterative redesign cycles to resolve late-stage thermal failures. To address these challenges, we propose 'ThermAl', a physics-informed generative AI framework which effectively identifies heat sources and estimates full-chip transient and steady-state thermal distributions directly from input activity profiles. ThermAl employs a hybrid U-Net architecture enhanced with positional encoding and a Boltzmann regularizer to maintain physical fidelity. Our model is trained on an extensive dataset of heat dissipation maps, ranging from simple logic gates (e.g., inverters, NAND, XOR) to complex designs, generated via COMSOL. Experimental results demonstrate that ThermAl delivers precise temperature mappings for large circuits, with a root mean squared error (RMSE) of only 0.71°C, and outperforms conventional FEM tools by running up to ~200 times faster. We analyze performance across diverse layouts and workloads, and discuss its applicability to large-scale EDA workflows. While thermal reliability assessments often extend beyond 85°C for post-layout signoff, our focus here is on early-stage hotspot detection and thermal pattern learning. To ensure generalization beyond the nominal operating range 25-55°C, we additionally performed cross-validation on an extended dataset spanning 25-95°C maintaining a high accuracy (<2.2% full-scale RMSE) even under elevated temperature conditions representative of peak power and stress scenarios.

continue to escalate with each generation of technology [1], [2]. The failure of Dennard scaling has dissolved the traditional transistor scaling-power balance, leading to chips that are increasingly constrained by thermal and reliability limits over pure performance [2]. To prevent overheating and thermal-induced failures, designers must integrate accurate temperature estimation and control mechanisms early in the design flow, enabling techniques such as clock gating, power gating, dynamic voltage and frequency scaling (DVFS), and task migration to operate effectively in real time [3]- [6]. Current thermal-analysis techniques fall into two groups: high-fidelity finite-element analysis (FEA) and coarse-grain models. FEA tools capture detailed heat-transfer physics but incur prohibitive runtimes and setup complexity for full-chip, iterative exploration. In contrast, coarse methods-from analytical RC networks to infrared imaging-compromise spatial resolution, missing fine-grain hotspots that drive localized failure modes [7], [8]. These trade-offs leave a pressing need for predictive methods that simultaneously deliver circuit-level accuracy, computational efficiency, and seamless integration into early-stage design.

Although crucial, circuit-level thermal estimates are challenging to make due to complex heat transfer coupled with non-uniform patterns of power dissipation within currentday microprocessors. Early integration of thermal predictions aids designers in keeping thermal constraints within reach and eliminating expensive redesigns. Early identification of potential hotspots streamlines development. Traditional approaches based on core-wise or functional-unit power measurements lack the resolution to capture fine-grained hotspot behavior [9]- [12]. Inverse thermal-map techniques recover power maps from thermal measurements via optimization and machine learning [13]- [20], but they struggle to generalize at circuit-level granularity when heat fluxes become highly localized.

FEM commercial tools provide high fidelity, high computational cost, and difficulty setting them up render them unsuitable for large-scale, real-time applications, and even optimized methods like HotSpot [31], Power Blurring [32], and PACT [33] grow costly at finer resolutions. Compact thermal models such as 3D-ICE [34] and MTA [35] improve runtime efficiency for stacked 3D ICs and architecture-level exploration, but their grid coarseness limits spatial accuracy for dense sub-block thermal variations.

More recently, there have been more advanced learningbased methods. One approach utilizes spatial Laplace transforms to identify heat sources [21], while another employs GANs to predict full-chip thermal maps from performance metrics [22]. Deep neural approaches like DeepOHeat [36] Activity Guided local heat map generation Generated Thermal Output As transistor density in modern microprocessors increases, traditional thermal estimation methods often struggle with complex heat dissipation, leading to inaccuracies in temperature profiling. While commercial FEM tools offer high fidelity, they can be too slow and computationally inefficient for full-chip modeling. Simultaneously, thermal cameras tend to lack the highresolution detail needed for analysis at the circuit level. ThermAl tackles these limitations by using a generative neural network to deliver fast and accurate thermal estimation. More importantly, it integrates easily into the design exploration stage of the GDS generation, allowing designers to identify and correct thermal hotspots early on. Thermal-sensitive flow can prevent numerous iterations of designs, induced by thermal failures discovered late in the process, and thus simplify the overall circuit optimization process.

have attempted to infer steady-state temperature fields directly from power distributions, yet they often rely on data-driven correlations without explicit physical grounding, leading to limited generalization under new boundary conditions or materials. However, these remain reliant on imprecise, coarsegrained analysis due to limitations of thermal camera resolution or imperfect power-thermal coupling.

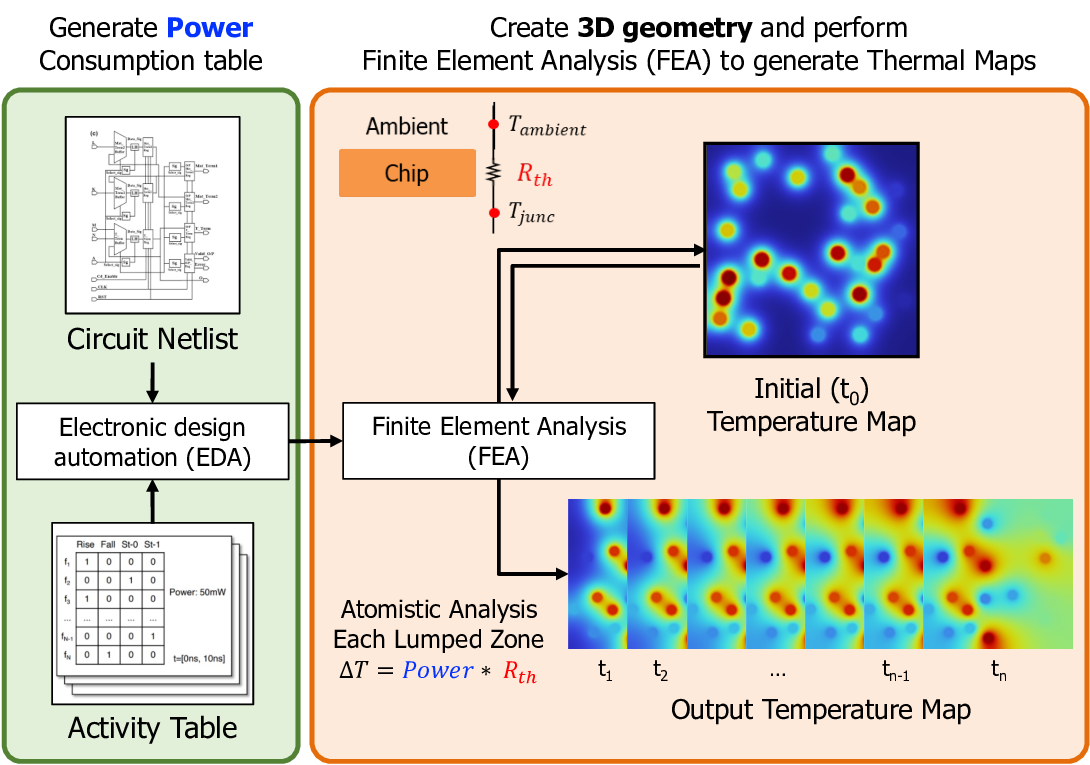

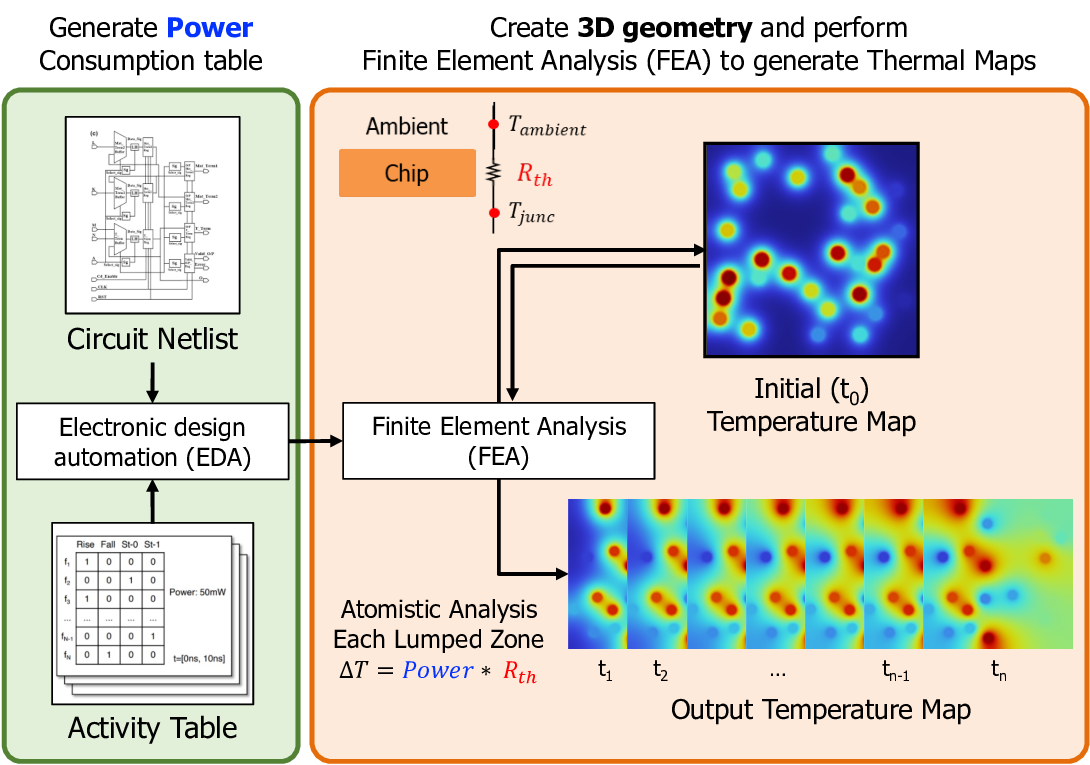

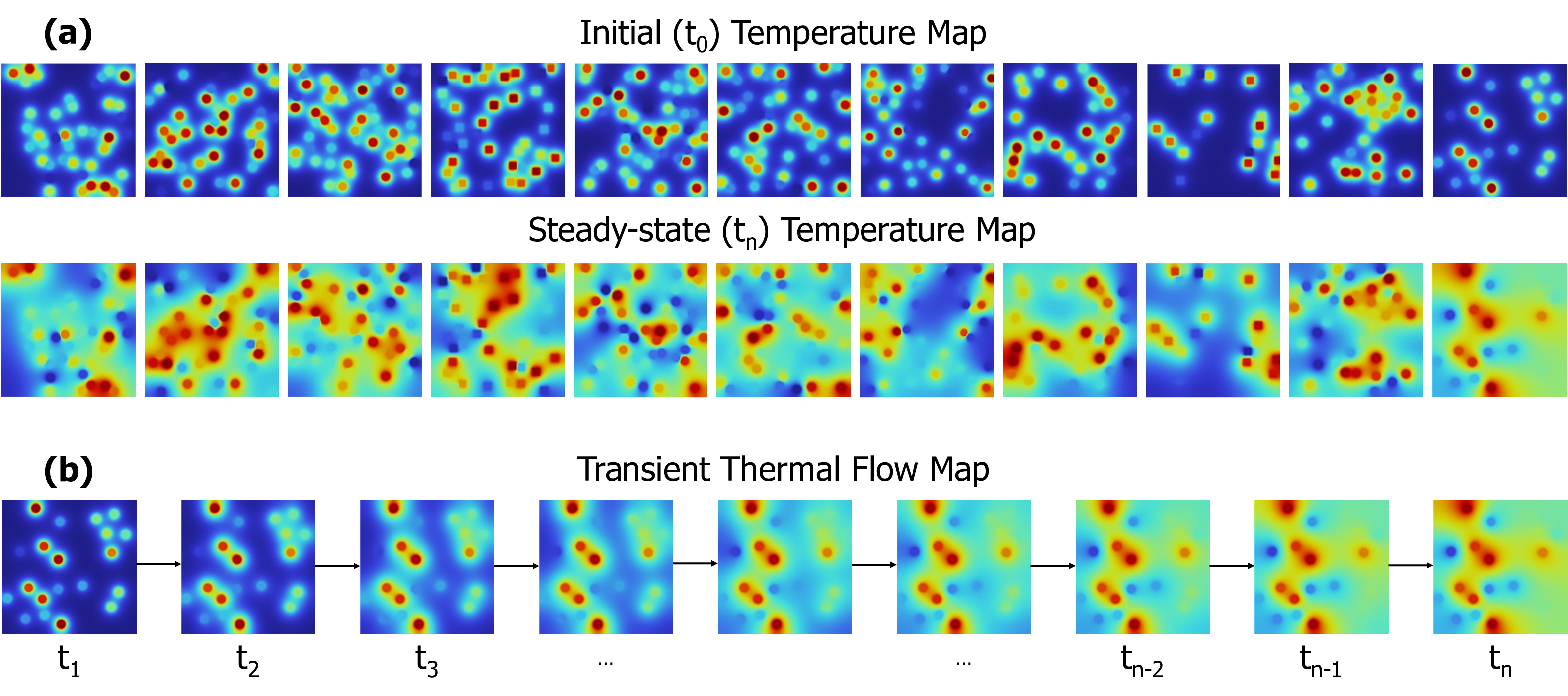

Moving beyond these challenges, we introduce a hybrid solution integrating detailed power estimation, circuit-level boundary values, and sophisticated thermal simulation. We integrate equivalent thermal RC networks [25], [26], architecture-level models [27], [28], and FEM methodologies [29] (Fig. 1) to accurately compute temperature gradients. We introduce ThermAl, a conditional generative framework that frames thermal analysis as an image-to-image translation task. The model generates steady-state and transient thermal maps by conditioning on a sample pair of images {E, E ′ }, capturing non-uniform heat dissipation, material heterogeneity, and dynamic boundary conditions.

Our dataset captures a wide spectrum of spatial and temporal activity patterns; however, the resulting thermal behavior is jointly

This content is AI-processed based on open access ArXiv data.