리셋 제어 시스템의 스케일드 그래프를 이용한 분석 및 설계

본 논문은 리셋 제어 시스템의 스케일드 그래프(SG)가 해당 시스템의 기본 선형 시스템(BLS)의 SG에 의해 상한으로 제한된다는 사실을 증명하고, 이를 기반으로 BLS의 SG만을 이용해 리셋 제어 루프의 안정성을 판단하는 새로운 조건을 제시한다. 또한 설계 절차를 제시하여 SG 기반 루프쉐이핑 방식으로 리셋 컨트롤러를 설계할 수 있게 한다.

저자: T. de Groot, W. P. M. H. Heemels, S. J. A. M. van den Eijnden

본 논문은 리셋 제어 시스템의 분석과 설계를 기존의 선형 시불변(LTI) 시스템 이론에 자연스럽게 연결시키는 새로운 방법론을 제시한다. 서론에서는 리셋 컨트롤러가 LTI 시스템의 근본적인 한계를 극복할 수 있는 잠재력을 가지고 있음에도 불구하고, 현재까지는 주파수 영역 기반의 복잡한 조건(예: 서클 기준, Hβ‑조건)이나 특정 구조에 제한된 해석만 가능하다는 문제점을 지적한다. 이러한 배경에서 최근 도입된 스케일드 그래프(SG) 개념을 활용하면 비선형 시스템도 Nyquist와 유사한 그래픽 방식으로 안정성을 판단할 수 있음을 소개한다.

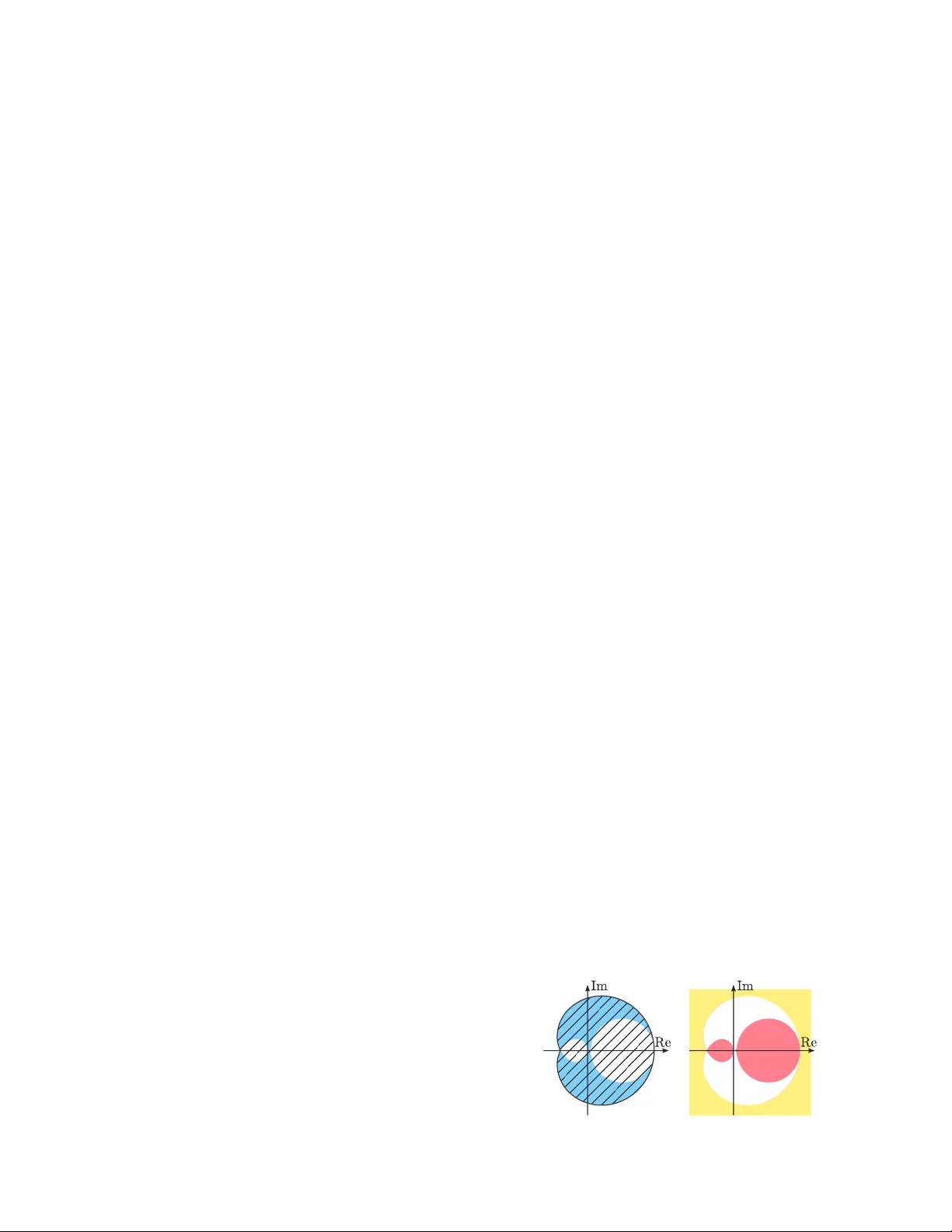

다음으로 SG와 관련된 기본 정의를 정리한다. 입력‑출력 신호 쌍 (u, y)에 대해 이득 ρ와 위상 θ를 정의하고, 이를 복소 평면에 ρ e^{±jθ} 형태로 매핑한 집합을 소프트 SG, 시간 구간을 고려한 하드 SG로 구분한다. SG는 시스템의 입력‑출력 특성을 전역적으로 포착하는 집합이며, 두 시스템의 부정 피드백 연결이 안정하려면 한 시스템의 SG와 다른 시스템의 SG가 일정 거리만큼 분리되어야 한다는 정리 1(Scaled‑Graph 기반 안정성 정리)을 제시한다. 이때 거리 조건만 만족하면 안정성을 보장하고, 추가로 chord property가 만족되면 L₂‑게인까지 평가할 수 있다.

본 논문의 핵심은 리셋 시스템 R(τ‑정규화 포함)의 SG가 그 기반 선형 시스템(R_BLS)의 SG에 의해 상한으로 제한된다는 정리 2이다. 여기서 R은 상태 방정식에 리셋 매핑 R·x와 타이머 τ를 포함하며, 리셋 조건은 M에 의해 정의된 집합 F와 J에 의해 결정된다. 정리 2는 먼저 LTI 시스템에 대한 Lemma 1을 이용해 SG를 다각형 혹은 원형 영역 S(Π)으로 과대근사하는 방법을 제시하고, 이를 통해 P∈S⁺_m을 찾는 LMI(8)를 구성한다. 이후 조건(14) ⟨P 0 RᵀP ½ 0 0 0 P ½ R 0 0⟩ + ⟨ρM 0 0 I_m⟩ ⪰ 0을 만족하면 SG(R)⊆patch(SG(R_BLS))가 성립한다. 여기서 patch 연산은 SG의 외부 비볼록 영역을 채워 ‘채워진’ 형태로 만든다. 특히 Corollary 1은 R=αI (α∈

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기