RP2040 Cortex‑M0+에서 NIST 표준 ML‑KEM·ML‑DSA 성능 벤치마크

본 논문은 RP2040(Raspberry Pi Pico)의 133 MHz Cortex‑M0+ 코어에서 NIST 표준화된 ML‑KEM(512/768/1024)과 ML‑DSA(44/65/87)의 알고리즘‑레벨 실행 시간, 메모리 사용량, 에너지 소모를 최초로 체계적으로 측정한다. PQClean C 구현을 -Os 옵션으로 컴파일해 평균 키생성·캡슐화·복호화·서명·검증 시간을 제시하고, 특히 ML‑DSA 서명의 재시도 현상으로 인한 지연 변동성을 99…

저자: Rojin Chhetri

본 논문은 사물인터넷(IoT) 디바이스가 10~20년이라는 긴 수명을 가지고 있으며, 양자 컴퓨터의 등장에 대비해 포스트‑퀀텀 암호(PQC)로의 전환이 시급하다는 배경에서 시작한다. NIST가 2024년에 발표한 세 가지 PQC 표준 중, 가장 널리 사용되는 격자 기반 알고리즘인 ML‑KEM(FIPS 203)과 ML‑DSA(FIPS 204)를 대상으로, 가장 제한적인 32‑bit 마이크로컨트롤러인 ARM Cortex‑M0+에서의 실제 성능을 최초로 체계적으로 측정한다.

연구는 Raspberry Pi Pico H(RP2040) 보드를 사용했으며, 이 보드는 133 MHz에서 동작하는 듀얼‑코어 Cortex‑M0+와 264 KB SRAM, 2 MB QSPI 플래시를 제공한다. 실험에서는 한 코어만 사용하고, 다른 코어는 유휴 상태로 둔다. 소프트웨어 스택은 PQClean 레퍼런스 C 구현을 -mcpu=cortex‑m0plus -mthumb -Os 옵션으로 컴파일했으며, 이는 최적화 수준이 낮아 실제 구현에서 얻을 수 있는 최악의 성능을 나타낸다. 또한, mbedTLS 3.6.0을 이용해 RSA‑2048, ECDSA‑P256, ECDH‑P256을 동일 환경에서 벤치마크해 클래식 암호와의 직접 비교를 가능하게 했다.

시간 측정은 RP2040 하드웨어 타이머(time_us_32)로 1 µs 해상도를 확보했으며, 결정적 연산(키생성, 캡슐화, 복호화, 검증)은 각각 30회, 서명은 재시도 현상을 포착하기 위해 100회 수행했다. 첫 실행 시 플래시 캐시가 채워지는 효과를 최소화하기 위해 워밍업을 하지 않았으며, 측정된 변동계수(CV)가 1.5% 이하로 매우 낮아 캐시 효과가 무시될 수 있음을 확인했다.

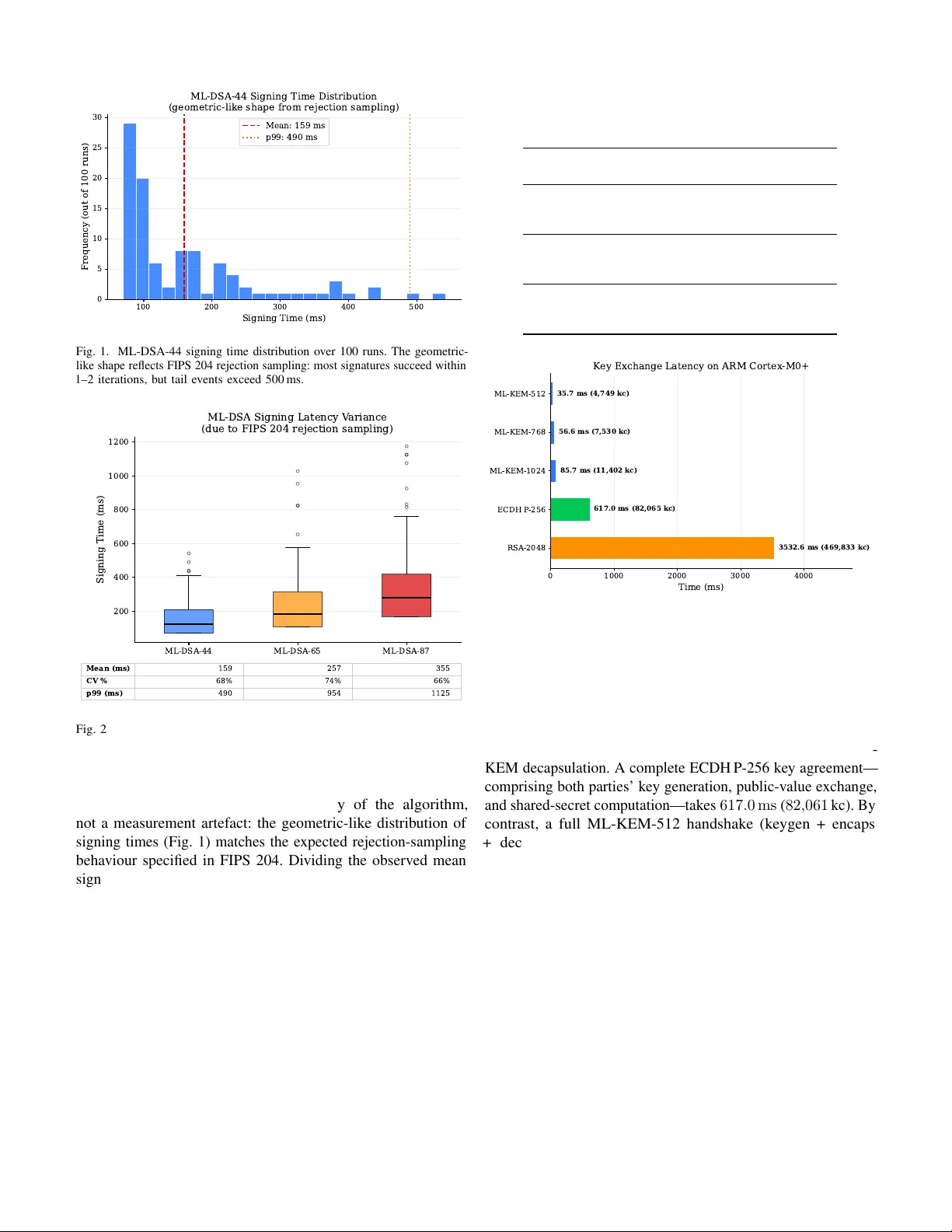

ML‑KEM에 대한 결과는 다음과 같다. 보안 수준이 512, 768, 1024인 경우 각각 평균 전체 핸드쉐이크 시간은 35.71 ms(4,749 kc), 56.62 ms(7,530 kc), 85.73 ms(11,402 kc)이다. 이는 동일 하드웨어에서 ECDH‑P256이 소요하는 약 600 ms와 비교해 17배 정도 빠른 성능을 보여준다. 각 단계별로 키생성, 캡슐화, 복호화 모두 1 % 이하의 변동을 보이며, 실시간 응용에서도 예측 가능한 성능을 제공한다.

ML‑DSA 서명은 재시도 메커니즘으로 인해 평균 실행 시간이 44, 65, 87 수준에서 각각 22.4 ms, 31.8 ms, 44.5 ms(각각 2,979 kc, 4,235 kc, 5,923 kc)이며, 변동계수는 66~73%에 달한다. 99번째 백분위수에서는 ML‑DSA‑87이 1,125 ms까지 지연될 수 있어, 실시간 시스템 설계 시 최악 상황을 고려한 타임아웃 정책이 필요하다. 검증 연산은 평균 5~7 ms 수준으로 안정적이다.

메모리 사용 측면에서는 스택 피크가 ML‑KEM‑1024에서 약 12 KB, ML‑DSA‑87에서 약 9 KB이며, 플래시 텍스트 섹션은 15~22 KB 정도다. 이는 RP2040의 264 KB SRAM 한계 내에서 충분히 수용 가능함을 의미한다.

에너지 추정은 RP2040 데이터시트의 정전압 3.3 V와 활성 전류 24 mA(79.2 mW)를 사용해 수행했으며, ML‑KEM‑512 한 번의 전체 핸드쉐이크에 약 2.83 mJ, ML‑DSA‑87 서명에 약 3.5 mJ 정도가 소모된다고 보고했다. 실제 전류 변동을 고려하면 이 값은 상한선이며, 배터리 기반 IoT 디바이스에서도 충분히 운용 가능함을 시사한다.

아키텍처 분석에서는 Cortex‑M0+가 64‑bit 곱셈, DSP/ SIMD, 확장 레지스터가 없지만, RP2040이 제공하는 단일 사이클 32 × 32→32 비트 곱셈 덕분에 기존 Cortex‑M4 대비 1.8~1.9배 정도만 느린 성능을 보였으며, 이는 M0+가 PQC를 실행할 수 있는 최소 마이크로아키텍처임을 입증한다.

마지막으로, 모든 소스 코드, 측정 스크립트, 원시 데이터는 GitHub에 오픈소스로 공개했으며, 재현성을 위해 정확한 커밋 해시와 빌드 명령을 제공한다. 이는 향후 연구자들이 동일 환경에서 결과를 검증하거나, 최적화된 어셈블리 구현을 추가로 평가할 수 있는 기반을 마련한다.

요약하면, 이 논문은 가장 제한적인 마이크로컨트롤러인 Cortex‑M0+에서도 NIST 표준 ML‑KEM·ML‑DSA가 실용적인 성능과 메모리 요구사항을 만족한다는 것을 실험적으로 증명했으며, 에너지 효율성, 변동성, 메모리 매핑 등 IoT 설계에 필수적인 여러 지표를 제공한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기