칩렛 기반 CPU GPU 통합을 위한 재생 구동 검증 방법론

** 본 논문은 ODIN 칩렛 아키텍처에 CPU, 다중 Xe GPU 코어 및 NoC를 통합하면서, 파형 캡처와 재생을 이용해 시뮬레이션과 에뮬레이션 양쪽에서 동일한 검증 흐름을 구현한 방법을 제시한다. 재생 엔진은 GPU 주변 인터페이스 신호를 사이클 정확도로 기록·ROM에 저장하고, 이를 재생함으로써 비결정적 요소를 제거하고 디버깅·통합 시간을 크게 단축한다. **

저자: Nij Dorairaj, Debabrata Chatterjee, Hong Wang

**

본 논문은 차세대 AI·그래픽 워크로드를 지원하기 위해 CPU와 다중 Xe GPU 코어, 그리고 고성능 NoC를 하나의 칩렛으로 통합하는 ODIN 아키텍처의 사전 실리콘 검증 방법을 제시한다. 전통적인 검증 흐름은 복잡한 인터페이스 프로토콜, 대규모 설계 규모, 높은 동시성, 그리고 비결정적 실행 특성 때문에 시뮬레이션과 에뮬레이션 사이에 별도의 모델·콜라테랄을 유지해야 하는 큰 부담을 안고 있다. 특히 GPU는 메모리‑입력·출력 중심의 실행 모델을 가지고 있어 NoC·메모리 컨트롤러와의 복잡한 트래픽 교환이 필수적이며, 이 과정에서 타이밍 의존성 및 순서 보장이 핵심 검증 포인트가 된다.

이를 해결하기 위해 저자들은 ‘Replay Engine’이라는 새로운 검증 프레임워크를 설계하였다. Replay Engine은 GPU IP 검증 단계에서 파형을 사이클‑정밀도로 캡처하고, 캡처된 파형을 오프라인 툴을 통해 인터페이스 신호와 응답을 추출해 비트스트림 형태로 변환한다. 변환된 데이터는 ROM 초기화 이미지로 가공되어 SoC 설계에 포함된다. 시뮬레이션 혹은 에뮬레이션 실행 시, Replay Engine은 이 ROM을 읽어 원본 파형과 동일한 타이밍에 신호를 재생함으로써 GPU 부팅 및 워크로드 실행을 재현한다.

Replay Engine의 주요 특징은 다음과 같다.

1. **비침투형 캡처**: GPU 주변 인터페이스만을 관찰하므로 기존 IP에 대한 구조적 변경이 필요 없으며, 기능적 정확성을 유지한다.

2. **단일 검증 콜라테랄**: 캡처된 파형을 ROM에 저장함으로써 시뮬레이션·에뮬레이션 모두에서 동일한 검증 데이터를 사용한다. 이는 BFM 기반 흐름에서 발생하던 모델·컴파일 차이를 제거한다.

3. **디버깅 효율성**: 시스템‑레벨 오류가 발생했을 때, 재현 가능한 사이클‑정밀 파형을 기반으로 IP 경계까지 디버깅 범위를 축소한다. 이는 전통적인 전면 디버깅에 비해 시간·노력을 크게 절감한다.

4. **증분 검증 지원**: 설계 변경(예: 로컬 IP 수정, 인터페이스 업데이트) 시 캡처만 다시 수행하면 되므로 검증 흐름을 재구성할 필요가 없다.

논문은 ODIN SoC의 전체 토폴로지를 상세히 설명한다. CPU 서브시스템은 Coherent IDI 링크를 통해 NoC에 연결되며, 전력 관리와 인터럽트/세마포어 제어 로직을 포함한다. GPU 서브시스템은 다중 Xe 코어와 실행 유닛(EU)으로 구성되며, 메모리‑드리븐 워크로드를 수행한다. GPU와 메모리 사이의 트래픽은 NoC를 통해 DDR·HBM 컨트롤러로 라우팅된다. 이러한 구조는 칩렛 간 모듈성을 높이고, 메모리 기술을 독립적으로 선택할 수 있게 한다.

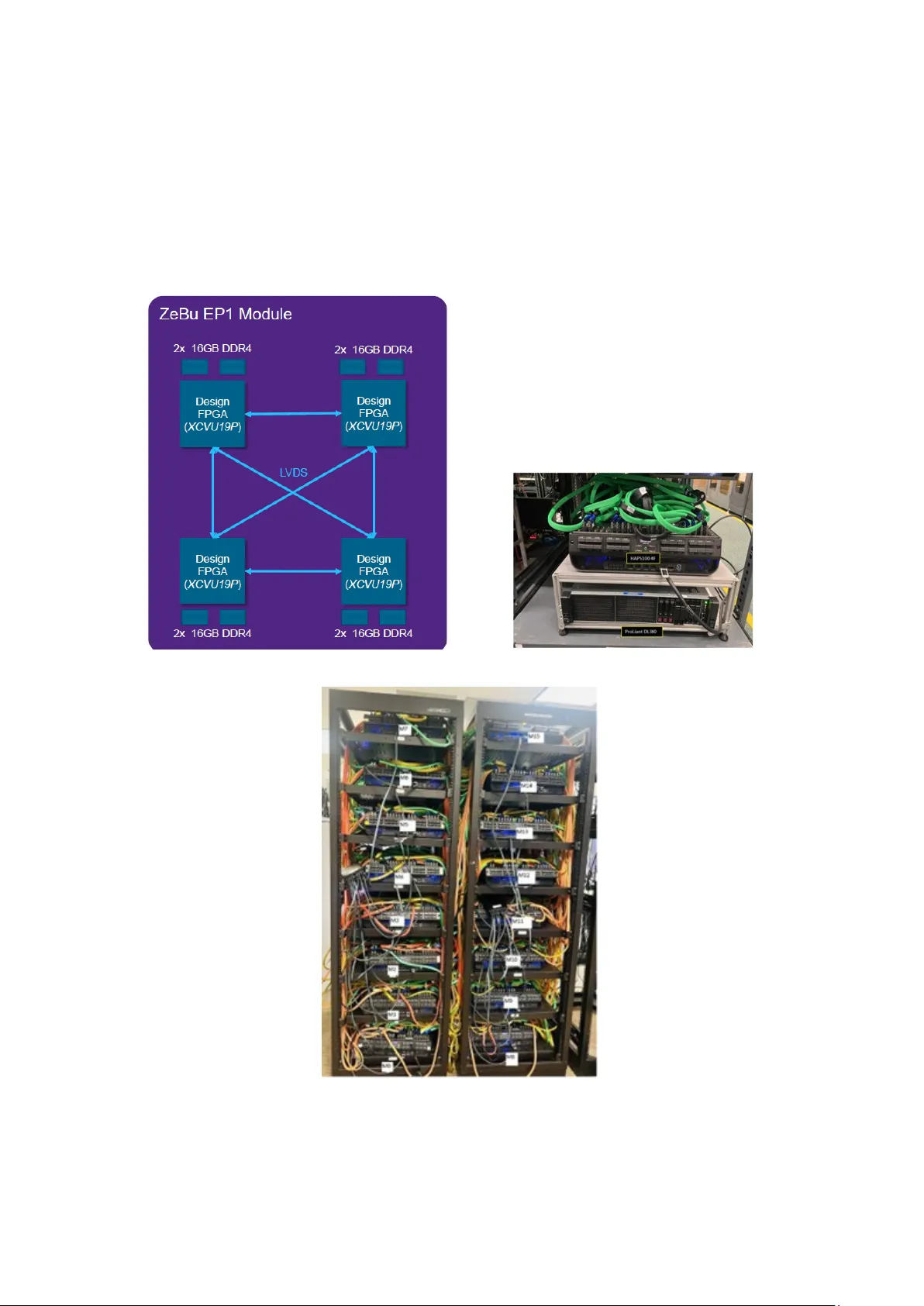

검증 흐름은 크게 두 단계로 나뉜다. 첫 번째는 **Replay Capture & ROM Initialization** 단계로, 독립적인 GPU IP 검증 환경에서 파형을 캡처하고, 이를 사이클‑정렬 비트스트림으로 변환해 ROM 이미지로 만든다. 두 번째는 **Simulation & Emulation** 단계이다. 시뮬레이션에서는 YAMl‑기반 설정과 동일 DB를 사용해 Replay Engine이 ROM을 읽어 파형을 재생하고, 상세 파형 가시성을 통해 부팅 시퀀스, 메모리 순서, 프로토콜 타이밍 등을 검증한다. 에뮬레이션에서는 동일 ROM을 이용해 고속 실행을 수행함으로써 전체 시스템 부팅 및 GPU 워크로드를 실시간에 가깝게 실행한다.

실험 결과는 다음과 같다. Replay‑driven 검증을 적용한 결과, 전체 CPU‑GPU‑NoC SoC가 한 분기 내에 부팅 및 첫 번째 GPU 워크로드 실행을 성공적으로 검증하였다. 시뮬레이션에서는 기대 파형과 비교해 정확히 일치했으며, 에뮬레이션에서는 리소스 사용량이 현재 보드 한계 내에 머물면서도 충분한 마진을 확보했다. 또한, 기존 BFM 기반 흐름 대비 검증 콜라테랄 유지 비용이 60 % 이상 감소했으며, 디버깅 사이클이 평균 4배 이상 단축되었다.

결론적으로, 논문은 파형 캡처·재생 기반 검증이 칩렛 기반 대규모 SoC의 사전 실리콘 검증에 있어 확장 가능하고 효율적인 방법임을 입증한다. 이 접근법은 비결정적 요소를 제거하고, 시뮬레이션·에뮬레이션 간 일관성을 보장함으로써 설계 주기 단축과 품질 향상에 크게 기여할 것으로 기대된다.

**

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기