III V 나노와이어와 포토닉 회로의 고효율 결합 아키텍처

초록

본 논문은 InAsP 양자점이 삽입된 InP 나노와이어를 Si₃N₄ 곡선형 및 분할형 파형가이드에 접합하여, 양쪽 단에서 단일광자를 효율적으로 추출하고 교차 상관 측정을 통해 양자점의 중성·양자·전하 복합체(X, XX, X⁻) 모두에서 단일광자 방출을 입증한다. 시뮬레이션과 실험을 결합해 탭퍼 설계가 결합 효율과 공정 내성에 미치는 영향을 분석하고, 나노와이어가 양방향 빔스플리터 역할을 수행함을 보였다.

상세 분석

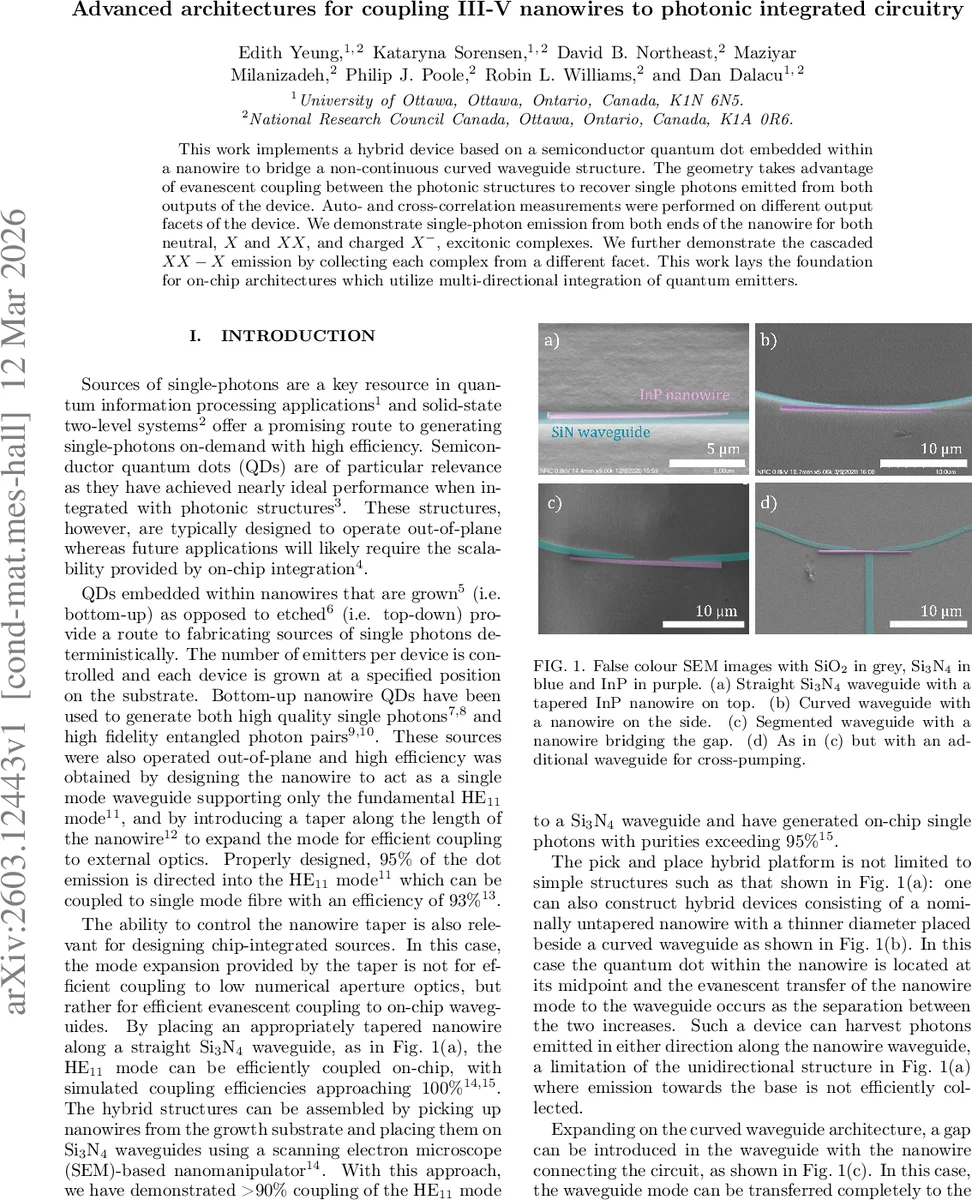

이 연구는 III‑V 반도체 나노와이어와 실리콘 기반 포토닉 집적 회로(Si₃N₄)의 결합 효율을 극대화하기 위한 구조적 혁신을 제시한다. 먼저, 저차원 전자기 시뮬레이션(FEM, COMSOL)으로 나노와이어 반경(rₙw)과 탭퍼 길이가 HE₁₁ 모드와 TE/TM 파형가이드 모드 간 전력 전달에 미치는 영향을 정량화하였다. 곡선형 파형가이드에 직접 접촉시키는 경우 rₙw≈115 nm에서 최대 76 %의 전력 전달이 관측되었으나, 반경 변동에 민감해 실험적 재현성이 낮았다. 반면, 파형가이드에 4 µm 간격의 갭을 두고 양쪽 끝을 2 µm 길이의 탭퍼로 연결한 ‘분할형’ 구조는 rₙw 변화에 대한 의존도가 크게 감소하고, TE·TM 양쪽 편광에 대해 90 % 이상의 전송 효율을 달성했다. 이는 탭퍼가 모드 변환을 점진적으로 진행시켜 급격한 굴절률 변화를 완화하고, 나노와이어와 파형가이드 사이의 에반에센트 결합을 최적화하기 때문이다.

실험적으로는 선택적 영역 증착(VLS)으로 성장된 InAsP 양자점을 중심에 배치한 InP 나노와이어(코어 20 nm, 전체 직경 210 nm, 길이 20 µm)를 SEM 기반 나노조작기로 픽‑앤‑플레이 방식으로 Si₃N₄ 파형가이드에 정확히 위치시켰다. 양자점은 나노와이어 중앙에 위치해 파형가이드 갭의 정중앙에 놓이게 되며, 이는 양쪽 파형가이드로의 대칭적 전력 분배를 기대한다. 실제 측정에서는 한쪽에서 펌프하고 반대쪽에서 수집했을 때 X, XX, X⁻ 피크가 각각 575 kcps, 330 kcps, 330 kcps(80 MHz 펄스)로 검출되어 전체 시스템 효율이 0.4–0.7 % 수준임을 확인했다. 손실은 주로 광학 경로(10 % 미만)와 양방향 수집 시 50 % 손실, 그리고 나노와이어‑파형가이드 결합 효율에 기인한다. 특히, 반대 방향에서의 수집 효율이 두 차수 낮게 나타난 것은 양자점이 갭 내에서 정확히 중앙에 위치하지 않았거나, 나노와이어 자체에 미세 탭퍼가 존재해 비대칭 결합을 초래했을 가능성을 시사한다.

시간분해 광발광(PL) 측정에서는 X와 X⁻가 긴 스핀플립 시간(τ_d≈16–18 ns)과 밝은 상태 수명(τ_b≈1.7–2.1 ns)을 보였으며, XX는 거의 단일 지수 감쇠(τ_b≈0.98 ns)와 짧은 스핀플립을 나타냈다. 이는 전하 상태에 따라 비복사 재결합 경로가 달라짐을 의미한다. 두 번째 차수 상관(g²(τ)) 측정에서는 X와 X⁻에서 g²(0)≈0.03–0.05(다중광자 확률 < 5 %)를, XX에서 g²(0)≈0.15(다중광자 확률 ≈ 15 %)를 기록했다. XX의 높은 다중광자 비율은 포화 펌프 전력과 빠른 재흥분(re‑excitation) 현상이 겹쳐 발생한 결과로 해석된다. 또한, 양쪽 파형가이드에서 동시에 수집함으로써 나노와이어가 내장형 비스플리터 역할을 수행함을 입증했으며, 이는 향후 다중채널 양자 네트워크 구현에 유용한 설계 원칙이 된다.

전반적으로, 이 논문은 (1) 탭퍼를 이용한 곡선형·분할형 파형가이드와 나노와이어의 에반에센트 결합 최적화, (2) 나노와이어 자체가 양방향 빔스플리터로 기능하는 다중출력 구조, (3) 다양한 양자점 복합체에 대한 고순도 단일광자 방출 검증이라는 세 가지 핵심 성과를 제시한다. 이러한 설계는 실리콘 포토닉 플랫폼에 III‑V 양자점 소스를 직접 통합하는 로드맵을 제공하며, 향후 온칩 양자 통신·컴퓨팅·센싱 시스템에 필수적인 다중채널, 고효율, 저손실 광원으로 활용될 전망이다.

댓글 및 학술 토론

Loading comments...

의견 남기기