FPPS FPGA 기반 포인트 클라우드 처리 시스템

초록

본 논문은 자율주행 차량의 3차원 인식 파이프라인에서 핵심적인 역할을 하는 ICP(Iterative Closest Point) 알고리즘을 FPGA로 가속화한 FPPS 시스템을 제안한다. KITTI 데이터셋을 이용한 평가 결과, 최고 35배, 평균 15.95배의 속도 향상을 달성했으며, 전력 효율은 8.58배 개선하였다. 정확도는 기존 CPU 기반 구현과 거의 동일하게 유지된다.

상세 분석

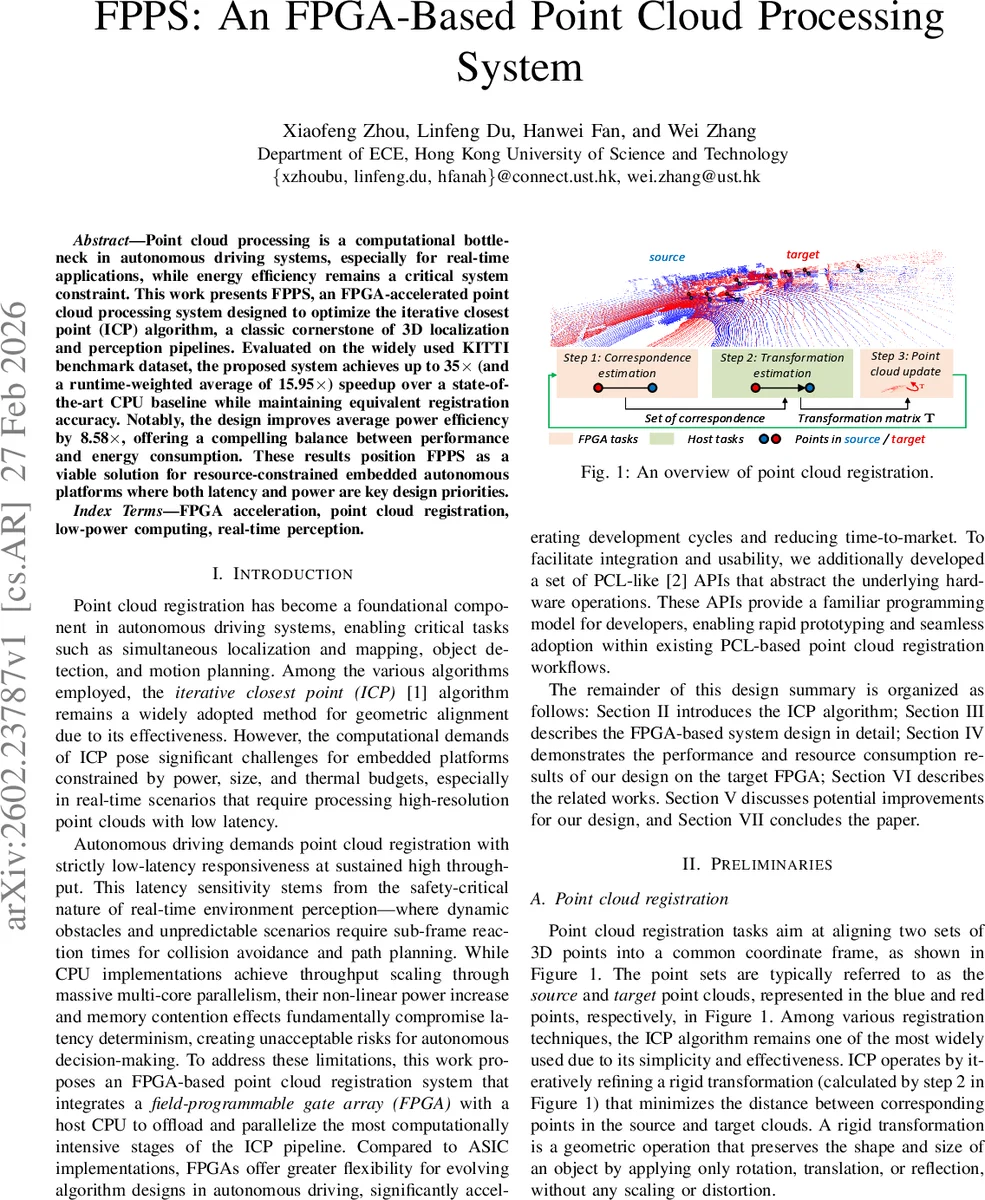

FPPS는 FPGA와 호스트 CPU가 협업하는 하이브리드 구조를 채택한다. 핵심 가속 대상은 ICP 알고리즘의 가장 연산 집약적인 단계인 최근접 이웃(NN) 탐색이며, 이를 위해 설계된 NN 서치 엔진은 스트리밍 파이프라인과 systolic array 기반의 완전 병렬 구조를 사용한다. 데이터는 BRAM에 저장된 소스 포인트와 타깃 포인트를 각각 레지스터 버퍼와 파티셔닝된 메모리 블록에 로드한 뒤, 거리 계산 유닛에서 동시에 다수의 후보 거리들을 계산한다. 최소값 선택은 비교 트리를 통해 실시간으로 수행되며, 결과는 바로 변환 행렬 추정 모듈로 전달된다.

변환 행렬 추정 단계에서는 누적된 공분산 행렬을 기반으로 SVD를 수행하는데, 이 연산은 FPGA 내부 DSP와 고정소수점 연산을 활용해 효율적으로 구현한다. 전체 파이프라인은 4단계(데이터 읽기 → 거리 계산 → 거리 비교 → 결과 누적)로 구성되어 각 단계가 FIFO로 연결돼 완전한 스트리밍 처리 흐름을 만든다. 이러한 설계는 메모리 접근 지연을 최소화하고, 온칩 BRAM을 활용해 외부 메모리 대역폭에 대한 의존성을 크게 낮춘다.

시스템은 AMD Alveo U50 보드(하나의 SLR에 구현) 위에 배치되었으며, 호스트는 11세대 Intel i5‑11400 CPU와 고성능 Xeon Gold 6246R을 각각 FPGA 가속 전후 비교에 사용하였다. 실험에서는 KITTI odometry 시퀀스 00~09을 대상으로 4096점 샘플링 후 전체 포인트 클라우드에 대해 최대 50번 반복 ICP를 수행하였다. 결과는 평균 RMSE가 0.01 m 이하 차이로 CPU와 동일함을 보여, 정밀도 손실이 없음을 확인했다.

성능 측면에서 FPPS는 시퀀스별 평균 프레임 지연을 3714 ms에서 162 ms까지 감소시켰으며, 가속 비율은 4.82×에서 35.36×까지 다양했다. 전력 소비는 FPGA 정적·동적 전력 28 W(정적 14 W, 동적 14 W)와 호스트 2.3 W를 합한 30.3 W이며, CPU 단독 실행 시 16.3 W 대비 8.58배 높은 performance‑per‑watt을 달성했다.

k‑d 트리 기반 NN 탐색이 순차적 의존성으로 인해 FPGA 파이프라인에 부적합하다는 분석도 포함된다. 대신 완전 병렬 systolic array 방식을 채택함으로써 결정론적 지연과 높은 처리량을 확보했다. 또한 PCL(Point Cloud Library)과 호환되는 API를 제공해 소프트웨어 개발자가 기존 코드베이스를 크게 수정하지 않고도 FPGA 가속을 활용할 수 있게 설계하였다.

요약하면, FPPS는 자율주행 시스템에서 요구되는 저지연·고정밀·저전력 3D 포인트 클라우드 정합을 FPGA 기반으로 실현했으며, 기존 연구 대비 가속률·전력 효율·프로그래머 친화성 모두에서 현저히 우수한 결과를 보여준다.

댓글 및 학술 토론

Loading comments...

의견 남기기