엣지 FPGA용 자동 CNN 변환 프레임워크 MING

초록

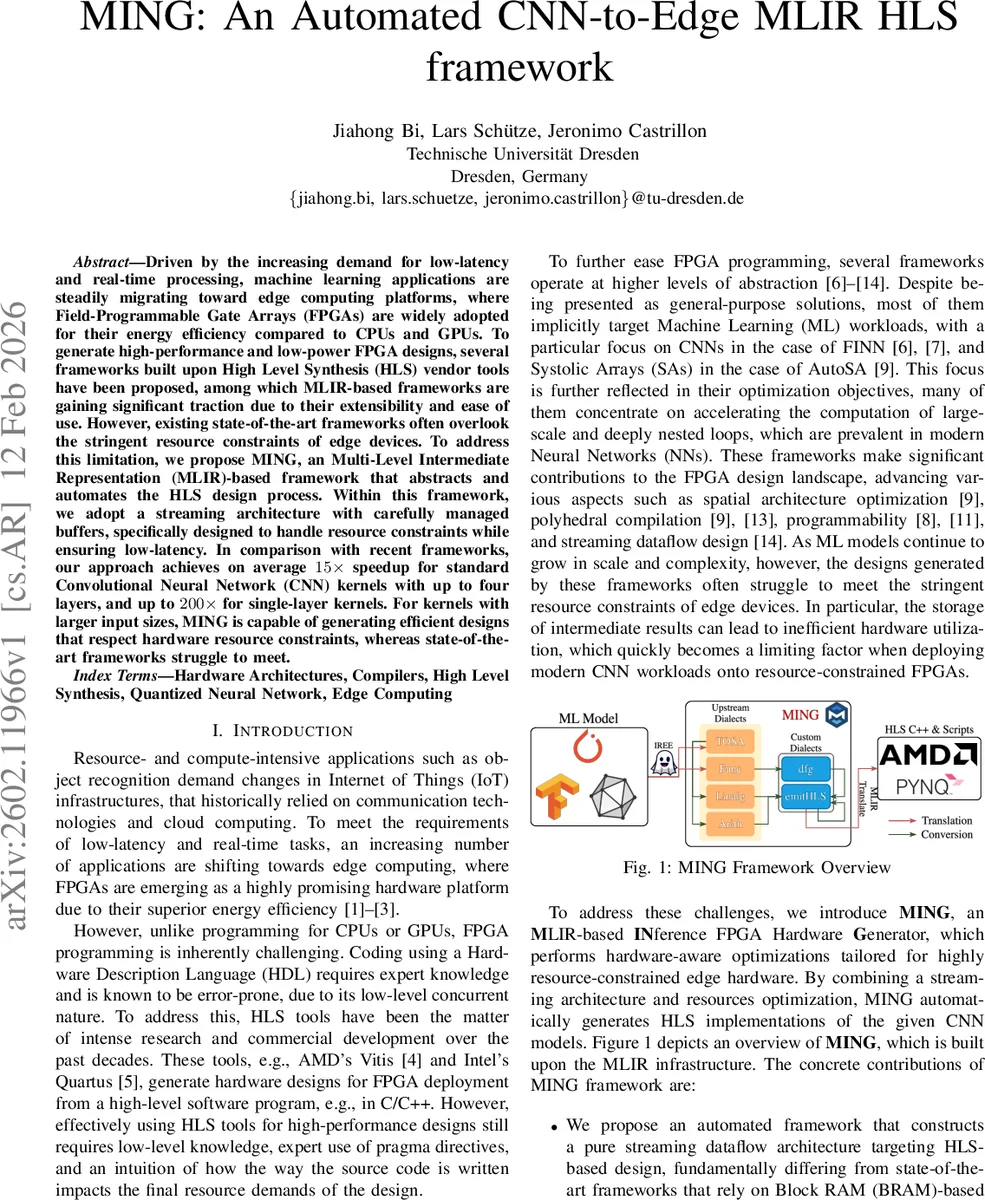

MING은 MLIR 기반의 자동화된 HLS 프레임워크로, 스트리밍 아키텍처와 버퍼 관리 기법을 통해 자원 제한이 심한 엣지 FPGA에서도 저지연 CNN 가속기를 구현한다. 기존 프레임워크 대비 평균 15배, 단일 레이어에서는 최대 200배의 속도 향상을 달성한다.

상세 분석

MING은 기존 MLIR 기반 HLS 프레임워크가 BRAM 등 온칩 자원을 과도하게 사용해 엣지 디바이스에 적용하기 어려운 문제를 근본적으로 해결한다. 핵심 아이디어는 완전 스트리밍 데이터플로우를 채택해 중간 텐서를 메모리에 저장하지 않고, 프로듀서‑컨슈머 간에 바로 스트림으로 데이터를 전달하는 것이다. 이를 위해 MING은 세 가지 커널 유형(순수 병렬, 정규 축소, 슬라이딩 윈도우)으로 linalg.generic 연산을 분류하고, 각 유형에 맞는 라인 버퍼와 FIFO 깊이를 자동으로 삽입한다.

프레임워크는 새로운 emitHLS dialect를 정의해 HLS 전용 pragma(UNROLL, PIPELINE, ARRAY_PARTITION, BIND_STORAGE 등)를 자동 삽입하고, 데이터플로우(dfg) dialect와 연계해 Kahn Process Network 모델을 구현한다. 설계 공간 탐색(DSE) 모듈은 MLIR 패스 안에서 동작하며, 주어진 BRAM, DSP, LUT 제한 하에 최적의 병렬도와 파이프라인 이니시에이션 인터벌(II)을 계산한다. 또한 정수 연산 기반의 자원 이용 모델을 제시해, 기존 폴리헤드리얼 기반 프레임워크보다 정확한 자원 예측을 제공한다.

실험 결과는 표준 CNN 커널(최대 4 레이어)에서 평균 15배, 단일 레이어에서는 최대 200배의 실행 시간 감소를 보여준다. 특히 입력 크기가 커질수록 기존 StreamHLS는 BRAM 사용량이 선형적으로 증가해 합성 불가능해지는 반면, MING은 라인 버퍼만 사용해 자원 한계를 넘어서는 설계도 성공적으로 합성한다. 이러한 장점은 저전력, 저비용 엣지 디바이스에 직접 배치 가능한 고성능 CNN 가속기를 제공한다는 점에서 큰 의미를 가진다.

댓글 및 학술 토론

Loading comments...

의견 남기기