마이크로아키텍처 클리프를 활용한 단일 특징 성능 벤치마크

초록

본 논문은 시뮬레이터와 RTL 사이의 미세한 동작 차이를 드러내는 “마이크로아키텍처 클리프(Microarchitecture Cliffs)”라는 벤치마크 생성 방법론을 제안한다. 클리프는 각 마이크로아키텍처 요소를 단일 특징으로 격리시켜 성능 차이를 정확히 귀속시킬 수 있게 하며, 자동화 도구와 함께 XiangShan 기반 gem5(XS‑GEM5)와 오픈소스 RTL(XS‑RTL) 간의 캘리브레이션에 적용해 오류를 59.2 %에서 1.4 %로 감소시켰다. 또한 SPECint2017/ SPECfp2017에서도 절대 오차를 크게 줄였다.

상세 분석

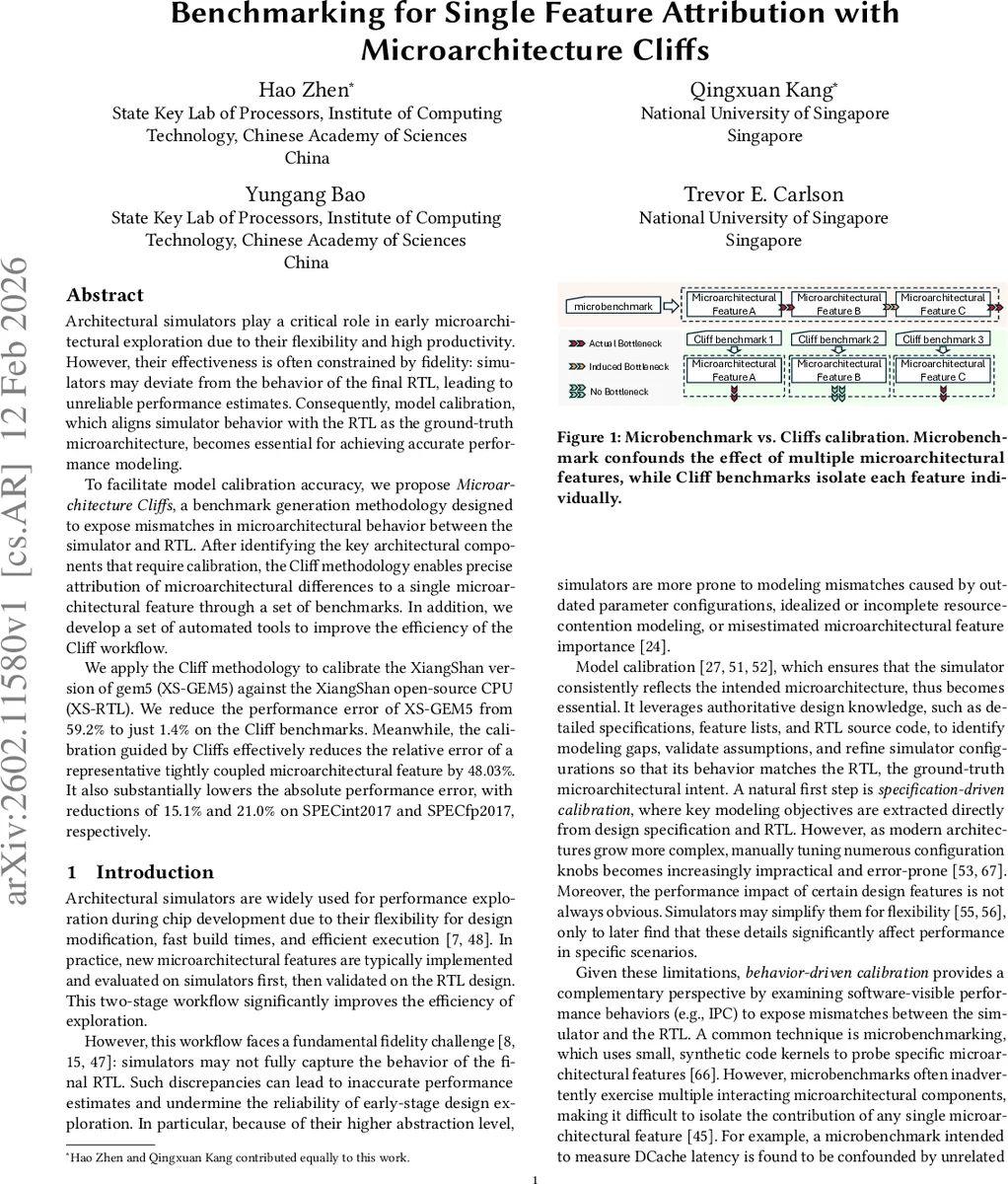

이 연구는 기존 마이크로벤치마크가 여러 마이크로아키텍처 요소를 동시에 활성화함으로써 원인 분석을 방해한다는 점을 지적한다. 저자들은 “클리프”라는 개념을 도입해, 성능 병목을 일으키는 특정 구조(예: ROB 할당, DCache 뱅크 충돌 등)를 고립시키는 일련의 벤치마크를 자동 생성한다. 핵심 아이디어는 (1) 성능 카운터를 클러스터링해 캘리브레이션이 필요한 컴포넌트를 우선순위화하고, (2) 우선순위에 따라 의존성을 최소화한 명령어 스니펫을 설계해 단일 특징만을 스트레스 테스트한다는 것이다.

클리프 벤치마크는 단계별 파이프라인 폭, ROB 크기, 메모리 파이프라인(LDPipe) 등 다양한 파라미터를 변화시켜 IPC 혹은 사이클 수의 비선형 응답을 관찰한다. 예를 들어, 기존 M‑I 마이크로벤치마크는 L1 DCache 대역폭 변화를 거의 감지하지 못했지만, 클리프는 파이프라인 폭을 1→3으로 늘릴 때 IPC가 0.6 %~0.7 %까지 명확히 증가함을 보여준다. 이는 특정 구조가 실제 성능에 미치는 영향을 정량화하는 데 큰 도움이 된다.

캘리브레이션 과정에서는 XS‑GEM5와 XS‑RTL 사이의 성능 차이를 클리프 벤치마크에서 59.2 %→1.4 %로 축소했다. 특히 Store‑Set 메모리 의존성 예측기의 경우, h264ref 워크로드에서 상대 오차를 48.03 % 감소시켰다. 이는 Store‑Set이 Nuke Replay, STA‑STD 분리 등 다중 연관 메커니즘에 의존함을 클리프가 정확히 파악했기 때문이다. 최종적으로 SPECint2017과 SPECfp2017에서도 절대 성능 오차를 각각 15.1 %와 21.0 % 줄이는 성과를 얻었다.

자동화 도구는 (a) 성능 카운터 기반 클러스터링, (b) 의존성 그래프 분석, (c) 코드 스니펫 자동 생성 및 컴파일 파이프라인을 포함한다. 이를 통해 대규모 마이크로아키텍처 설계에서 수백 개의 파라미터를 일일이 손수 조정하는 비용을 크게 절감한다.

이 논문의 주요 기여는 다음과 같다. 첫째, 단일 특징에 대한 정확한 성능 귀속이 캘리브레이션 정확도를 크게 향상시킨다는 실증적 증거를 제공한다. 둘째, 클리프 방법론과 자동화 툴 체인을 제시해 복잡한 최신 아키텍처(예: XiangShan)의 시뮬레이터와 RTL 간 차이를 체계적으로 줄일 수 있음을 보여준다. 셋째, 기존 마이크로벤치마크와 비교해 클리프가 더 높은 감도와 해석력을 제공함을 실험적으로 입증한다.

전반적으로 이 연구는 아키텍처 시뮬레이터의 신뢰성을 높이는 새로운 벤치마크 설계 패러다임을 제시하며, 향후 다양한 프로세서 아키텍처와 시뮬레이터에 적용 가능한 일반화된 캘리브레이션 프레임워크로 확장될 가능성을 시사한다.

댓글 및 학술 토론

Loading comments...

의견 남기기