고속 하이브리드 전압 레벨시프터를 이용한 캐스코드 클래스‑D 파워앰프의 엣지 불일치 및 출력 전력 저하 분석

초록

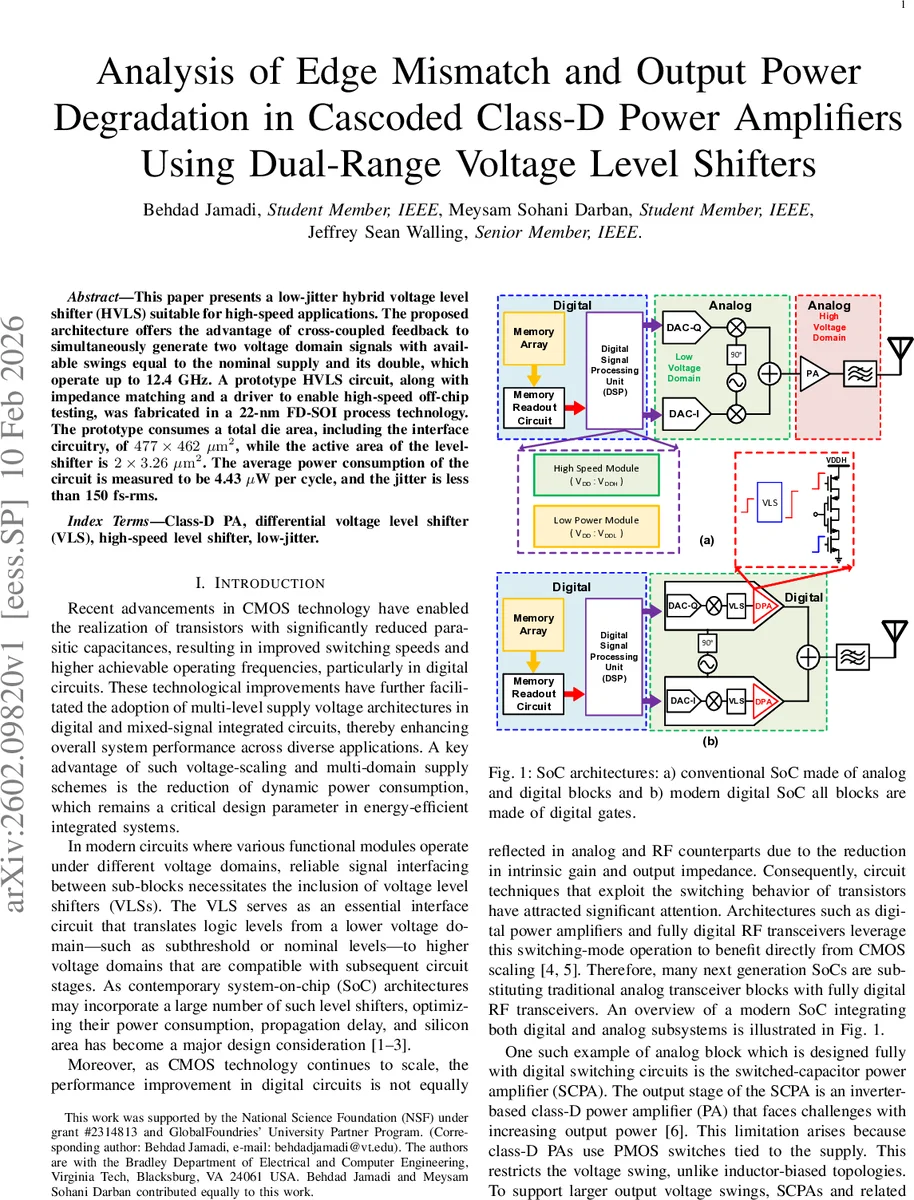

본 논문은 22 nm FD‑SOI 공정으로 구현한 저지터 하이브리드 전압 레벨시프터(HVLS)를 제안한다. 교차 결합 피드백을 이용해 VDD와 2·VDD 두 전압 레벨을 동시에 생성하며, 12.4 GHz까지 동작한다. 제안 회로는 4.43 µW·cycle 전력을 소모하고 지터가 150 fs 이하이다. 또한 캐스코드 구조의 클래스‑D 파워앰프에서 PMOS·NMOS 구동 신호의 지연 불일치가 출력 전력을 어떻게 감소시키는지를 수식으로 분석하고, HVLS가 이를 최소화함을 보인다.

상세 분석

본 연구는 최신 22 nm FD‑SOI 기술을 기반으로 하이브리드 전압 레벨시프터(HVLS)를 설계·실현한 점에서 의미가 크다. 기존 DCVS, CM, WCMLS와 같은 전통적인 레벨시프터는 각각 풀‑업·풀‑다운 전류 불균형, 정전 전류, 출력 전류 제한 등으로 인해 고속 동작 시 전력·지연 트레이드오프가 심했다. 저자는 이러한 문제점을 교차 결합 피드백 구조와 전류 제한 트랜지스터를 결합한 하이브리드 토폴로지를 제안함으로써, 풀‑업과 풀‑다운 경로 사이의 경쟁 전류를 크게 감소시켰다. 결과적으로 정전 전류가 거의 없으며, 전압 스윙이 VDD와 2·VDD 두 레벨을 동시에 제공한다.

시뮬레이션 및 실험 결과는 HVLS가 12.4 GHz까지 동작하면서 평균 전력 소모가 사이클당 4.43 µW, 지터가 150 fs‑rms 이하임을 보여준다. 이는 동일 공정에서 구현된 기존 레벨시프터 대비 1~2 order magnitude 낮은 전력과 10배 이상 향상된 주파수 대역을 의미한다.

논문은 또한 캐스코드 클래스‑D 파워앰프에서 PMOS와 NMOS 스위치 구동 신호의 지연 불일치(δt)가 출력 전력에 미치는 영향을 정량적으로 분석한다. 이상적인 스위치 모델에서는 출력 전력이 P_out,i = (8/π²)·V_DD² /R_opt 로 표현되며, 지연 불일치가 존재하면 P_out,ni = P_out,i·

댓글 및 학술 토론

Loading comments...

의견 남기기