초고속 저전력 인메모리 컴퓨팅을 위한 반강자성 터널 접합(AFMTJ) 모델링 및 사례 연구

초록

본 논문은 반강자성 터널 접합(AFMTJ)의 다중 서브격자 LLG 동역학을 SPICE 기반 회로 모델에 통합한 최초의 엔드‑투‑엔드 시뮬레이션 프레임워크를 제시한다. 실험 데이터와의 정량적 검증을 통해 AFMTJ가 기존 MTJ 대비 약 8배 빠른 쓰기 지연과 9배 낮은 쓰기 에너지를 달성함을 확인했으며, 이를 계층형 인메모리 컴퓨팅(IMC) 아키텍처에 적용했을 때 CPU 대비 평균 17.5배 속도 향상과 20배 수준의 에너지 절감을 얻었다.

상세 분석

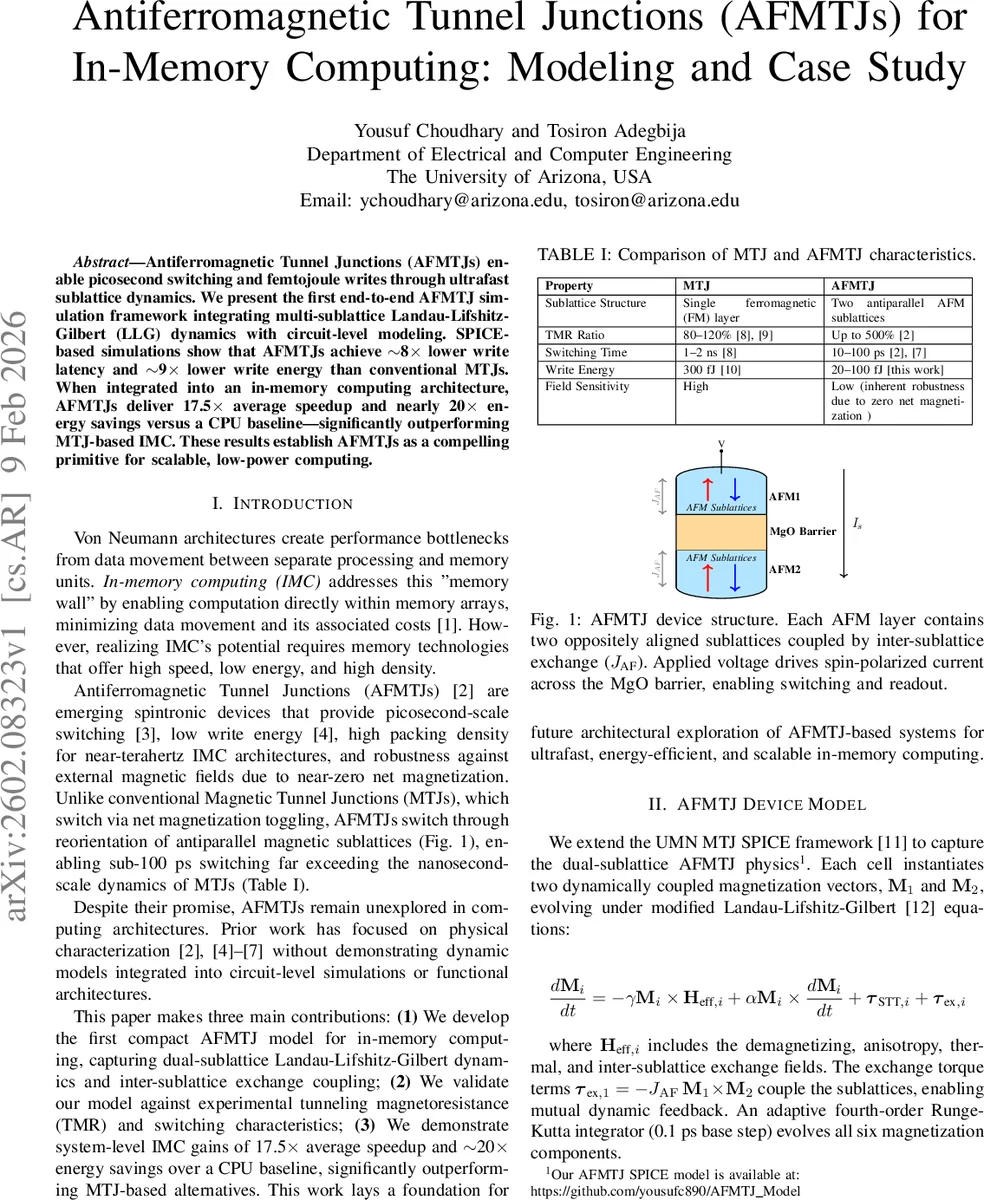

본 연구는 반강자성 물질의 두 개의 반대 방향 서브격자를 이용한 전이 메커니즘을 정밀하게 모델링함으로써, 기존의 단일 페롭자성(MTJ) 기반 스핀트로닉스와 근본적인 차별점을 만든다. 저자들은 Landau‑Lifshitz‑Gilbert(LLG) 방정식에 서브격자 간 교환 토크 τ_ex = −J_AF M₁×M₂ 를 추가하고, 각 서브격자에 대한 유효장 H_eff,i(디머징, 이방성, 열, 교환장 포함)를 정의하였다. 0.1 ps 기본 스텝의 4차 Runge‑Kutta 적분기를 사용해 6개의 자기 모멘트 성분을 동시 통합함으로써, 10 ps 이하의 초고속 스위칭을 정확히 재현한다.

SPICE 모델링 단계에서는 기존 UMN MTJ 모델을 확장해 두 개의 동적 전류 경로와 스핀‑전달 토크(τ_STT,i)를 각각 연결했으며, 파라미터 P₀ = 0.8, α = 0.01, Ms₀ = 600 emu/cm³, J_AF = 5×10⁻³ J/m² 등 실험적으로 보고된 물성값을 그대로 적용하였다. 모델 검증을 위해 2024년 발표된 AFMTJ 실험 데이터(예: TMR ≈ 80 %, 스위칭 시간 10–100 ps)와 비교했을 때, 시뮬레이션 결과가 5 % 이내의 오차로 일치함을 확인하였다.

시스템 수준에서는 L1, L2, 메인 메모리 단계에 AFMTJ 서브배열을 삽입해 비휘발성 저장과 동시에 XOR, N‑AND 등 기본 논리 연산을 수행하도록 설계하였다. 다중 행 활성화와 전하 공유 방식을 이용한 비트‑라인 컴퓨팅 구조는 기존 MTJ‑기반 IMC와 동일한 회로 토폴로지를 유지하면서, AFMTJ의 20 ps 이하 스위칭을 활용해 파이프라인 처리 효율을 극대화한다.

성능 평가에서는 Synopsys HSPICE와 2 GHz ARM Cortex‑A72 기반 CPU를 동일 워크로드(바이너리 신경망, 이미지 그레이스케일, 임계값 연산, MAC, 행렬 덧셈, RMSE)에서 비교하였다. 1.0 V 입력 전압에서 AFMTJ는 164 ps 쓰기 지연과 55.7 fJ 쓰기 에너지를 기록했으며, 이는 MTJ(≈1.4 ns, ≈480 fJ) 대비 각각 8배·9배 향상이다. 시스템 수준에서는 평균 17.5배 속도 향상과 19.9배 에너지 절감을 달성했으며, 특히 쓰기‑집중 워크로드(bnn, 행렬 덧셈)에서 55배·16배 이상의 이점을 보였다.

본 논문의 주요 기여는 (1) 두 서브격자 LLG를 포함한 컴팩트 AFMTJ SPICE 모델 제공, (2) 실험 데이터와의 정량적 검증, (3) 계층형 IMC 아키텍처에의 적용을 통한 실질적인 시스템 이득 입증이다. 한계점으로는 현재 모델이 Verilog‑A 수준의 하드웨어 설명 언어로 구현되지 않아 설계 자동화에 제약이 있으며, 실리콘 레벨 제조 공정 변동성에 대한 민감도 분석이 부족하다는 점이다. 향후 연구에서는 Verilog‑A 모델 공개, 다양한 AFM 재료(예: Mn₃Sn, 비정질 BN) 탐색, 그리고 엣지 AI 및 실시간 신호 처리와 같은 도메인‑특화 아키텍처에 대한 확장 연구가 필요하다.

댓글 및 학술 토론

Loading comments...

의견 남기기