FP8 연산 효율을 극대화하는 동적 비트폭 예측 기반 디지털 CIM 설계

초록

본 논문은 FP8 포맷의 가변 맨티사 비트폭을 지원하기 위해, 동적 Shift‑Aware Bitwidth Prediction(DSBP)과 FIFO 기반 입력 정렬 유닛(FIAU), 그리고 가변 정밀도 INT MAC 배열을 결합한 디지털 Compute‑in‑Memory(D CIM) 가속기를 제안한다. 28 nm 공정의 64 × 96 SRAM 매크로에 구현된 설계는 고정 E5M7 모드에서 20.4 TFLOPS/W를 달성하고, Llama‑7B 모델의 BoolQ·Winogrande 벤치마크에서 정확도 손실 없이 2.8배 이상의 에너지 효율 향상을 보인다.

상세 분석

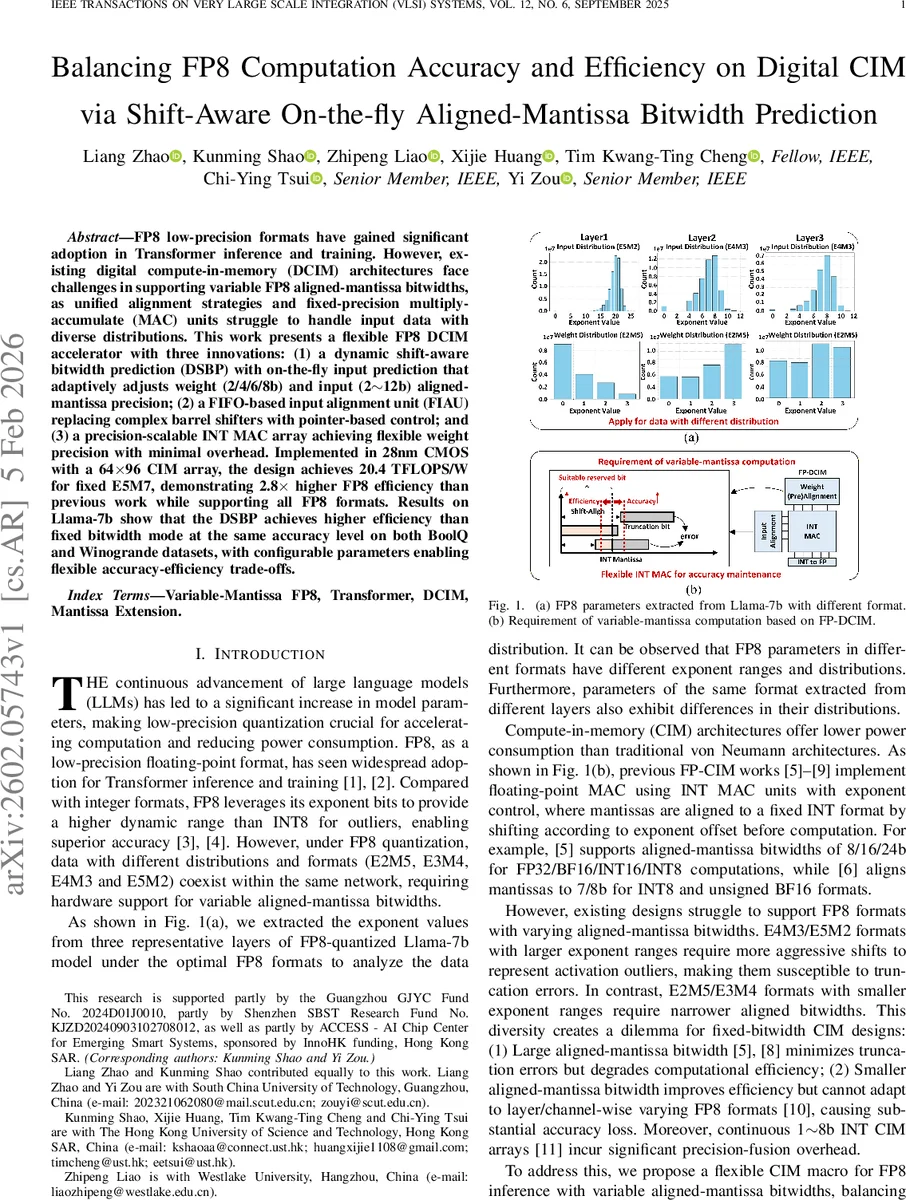

이 연구는 FP8 양자화가 Transformer 모델에서 널리 채택되는 현 상황에서, 서로 다른 지수 범위를 갖는 E2M5, E3M4, E4M3, E5M2와 같은 포맷이 동일 네트워크 내에 혼재함을 지적한다. 기존 디지털 CIM 설계는 고정된 맨티사 정렬 비트폭(예: 8/16/24 b)과 고정‑정밀도 MAC 유닛을 사용해 다양한 지수 오프셋을 처리하려다 보면, 큰 비트폭을 사용하면 전력·면적이 과다하고, 작은 비트폭을 사용하면 트렁케이션 오류가 급증해 정확도가 크게 저하된다. 이를 해결하기 위해 저자는 세 가지 핵심 기술을 도입한다. 첫째, DSBP 알고리즘은 그룹 단위(64 개 원소)로 지수 차이를 계산하고, 가중치와 입력 각각에 대해 동적으로 정렬 비트폭을 예측한다. 여기서 ‘shiftᵢ’ 값은 각 원소의 지수 차이를 나타내며, 이를 가중 평균하여 동적 비트폭 B_g_dyn을 산출하고, 사전에 정의된 스케일 팩터 k와 고정 비트폭 B_fix을 조합해 최종 비트폭을 결정한다. 이 과정은 하드웨어 친화적인 라운드‑업 방식을 사용해 2 ~ 12 b 입력, 2/4/6/8 b 가중치 정밀도를 제공한다. 둘째, MPU는 64개의 shiftᵢ를 3‑단계 파이프라인으로 처리해 실시간으로 B_g 값을 계산한다. 64‑입력 가산 트리와 8 b 역수 LUT를 활용해 연산량을 최소화하고, 동적 모드에서는 전체 매크로 면적의 7 %만 차지한다. 셋째, FIAU는 전통적인 배럴 쉬프터를 대체해 포인터 기반 FIFO 구조로 맨티사를 정렬한다. 입력을 2’s complement 형태로 MSB부터 순차 기록하고, 읽기 포인터를 지수 오프셋만큼 지연시켜 오른쪽 쉬프트 효과를 구현한다. 이 설계는 배럴 쉬프터 대비 21.7 % 면적, 34.1 % 전력 절감 효과를 보이며, 가변 비트폭 지원에 필요한 복잡한 조합 논리를 크게 단순화한다. 마지막으로, 가변 정밀도 INT MAC 배열은 2 ~ 12 b 입력과 2/4/6/8 b 가중치를 지원하도록 설계되었으며, 6 b 가중치 모드에서는 3개의 64 × 2 b MAC 결과를 합치는 전용 경로를 추가해 오버헤드를 최소화한다. 전체 매크로는 0.052 mm² 면적에 0.6 ~ 0.9 V, 50 ~ 250 MHz 동작 범위를 갖는다. 실험 결과, DSBP를 적용한 ‘Precise’(k=1, B_fix=6/5)와 ‘Efficient’(k=2, B_fix=4/4) 두 설정이 각각 평균 I/W 7.65/6.61 b와 5.58/6.08 b를 달성했으며, 전력 효율은 22.5 TFLOPS/W에서 33.7 TFLOPS/W까지 상승했다. 특히 Llama‑7B의 BoolQ·Winogrande 정확도는 FP8 기준(75.0 %/70.1 %)과 거의 동일하게 유지되면서, 고정 비트폭 대비 1.5 ~ 2 배 이상의 에너지 효율을 제공한다. ResNet‑18 이미지넷 실험에서도 동일한 트렌드가 확인돼, 제안 기법이 다양한 모델·데이터셋에 일반화 가능함을 입증한다.

댓글 및 학술 토론

Loading comments...

의견 남기기