통합 그래프로 자유로운 시스템 스택 시뮬레이션

초록

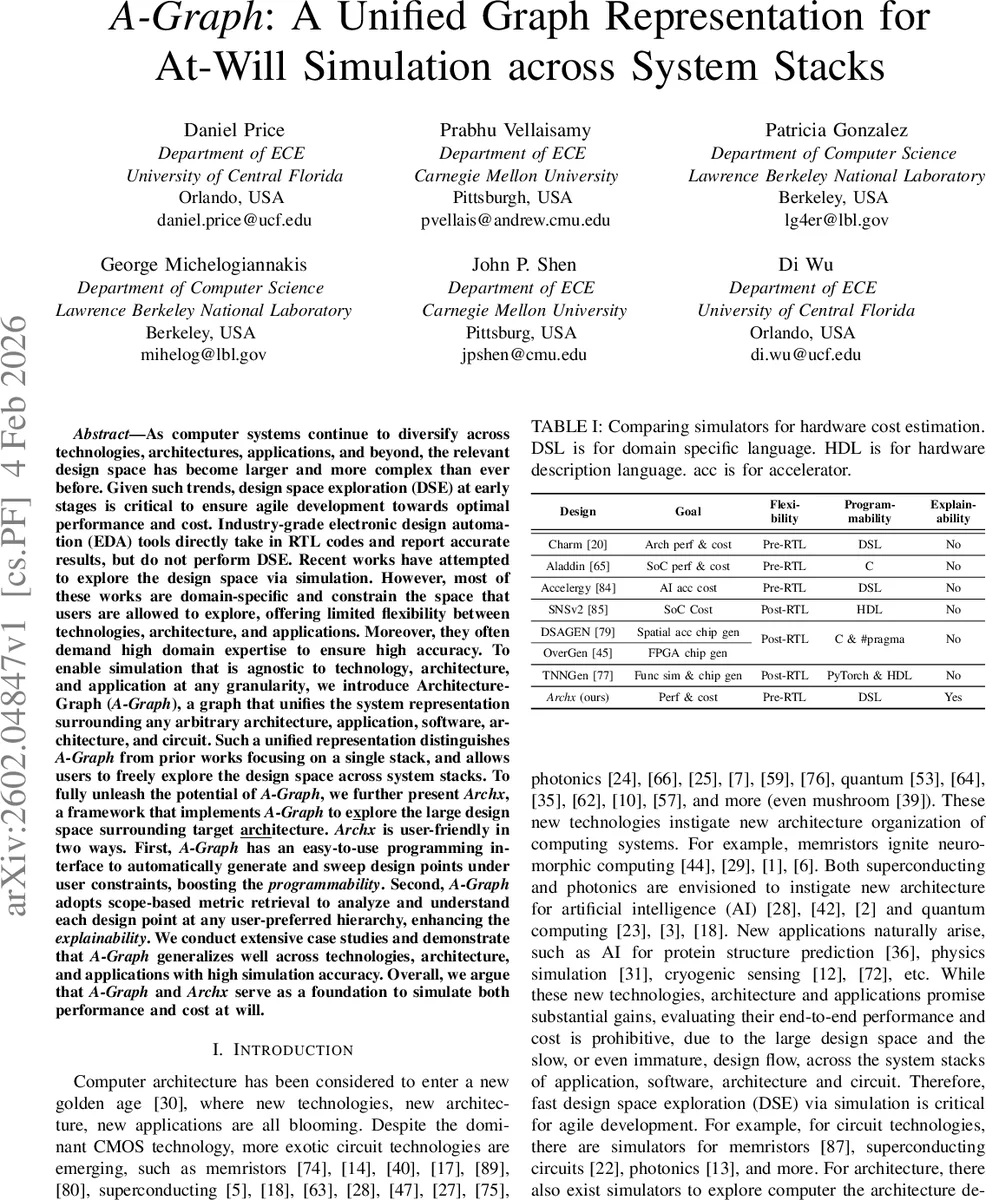

A‑Graph는 응용‑소프트웨어‑아키텍처‑회로 4계층을 하나의 가중치 방향 비순환 그래프로 통합한 표현 방식이다. 이를 구현한 Archx 프레임워크는 사용자 정의 제약 하에 설계점들을 자동 생성·스윕하고, 계층별 스코프 기반 메트릭을 추출해 성능·비용을 높은 정확도로 예측한다. 기존 시뮬레이터가 한 스택에 국한되던 문제를 넘어, 기술·아키텍처·응용 전반에 걸친 설계 공간을 자유롭게 탐색할 수 있다.

상세 분석

A‑Graph의 핵심은 Weighted Directed Acyclic Graph(WDAG)이며, 노드는 시스템 이벤트, 엣지는 이벤트 간 의존성을 가중치(예: 연산 수, 데이터 전송량)로 표현한다. 네 개의 추상화 레이어(응용, 소프트웨어, 아키텍처, 회로)가 수직적으로 쌓여 있어, 상위 레이어의 변화가 하위 레이어에 자동으로 전파된다. 응용 레이어는 워크로드를 루트 노드로 정의하고, 소프트웨어 레이어에서 이벤트를 세분화·재사용 가능하게 배치한다. 여기서 각 이벤트는 자체 성능 모델을 갖고, 입력 워크로드 특성과 아키텍처 모듈 파라미터를 이용해 하위 이벤트 가중치를 계산한다. 아키텍처 레이어는 모듈 계층 구조와 파라미터(예: 파이프라인 깊이, 메모리 대역폭)를 제공하며, 회로 레이어는 기술‑특정 메트릭(면적, JJ 수, 전력 등)을 노드에 매핑한다.

이러한 설계는 기존 시뮬레이터가 데이터 흐름, 제어 흐름, 혹은 아키텍처 의존성 중 하나만 모델링하던 한계를 극복한다. 가중치 엣지는 복합 의존성을 한 번에 표현하므로, 예를 들어 MAC 연산 하나가 여러 곱셈·덧셈 이벤트를 포함하는 경우를 자연스럽게 모델링한다. 그래프가 비순환이므로 위상 정렬을 통해 deterministic하게 메트릭을 집계할 수 있다.

Archx는 A‑Graph를 프로그래밍 인터페이스로 노출한다. 사용자는 DSL‑유사 스크립트로 레이어별 노드·엣지를 선언하고, 설계 제약(예: 최대 전력, 최소 성능)과 탐색 범위(예: 기술 선택, 모듈 파라미터)를 지정한다. 프레임워크는 제약을 만족하는 설계점들을 자동으로 생성하고, 각 설계점에 대해 그래프를 순회하며 정의된 메트릭을 계산한다. 메트릭은 “스코프 기반”으로 추출되는데, 이는 사용자가 원하는 계층(예: 모듈 수준, 서브시스템 수준)에서 집계값을 바로 얻을 수 있음을 의미한다. 따라서 설계자는 전체 시스템 수준의 KPI뿐 아니라, 특정 모듈이나 회로 레벨에서 발생하는 병목을 빠르게 파악한다.

논문에서는 CMOS와 초전도(SFQ) 두 기술, 이진·신경형 아키텍처, 그리고 신호 처리·GEMM 응용을 대상으로 케이스 스터디를 수행했다. 결과는 기존 RTL‑기반 EDA 툴과 비교했을 때 5~10% 이내의 성능·면적 오차를 보이며, 시뮬레이션 시간은 수 초 수준으로 크게 단축되었다. 특히 초전도 회로에서는 면적을 JJ 수로, 전력을 펨토와트 단위로 정확히 매핑해 기존 툴이 제공하지 못한 기술‑특화 메트릭을 제공한다.

핵심 인사이트는 다음과 같다. 첫째, 시스템 스택을 통합 그래프로 표현함으로써 설계 공간을 “자유롭게” 탐색할 수 있다. 둘째, 가중치 기반 의존성 모델은 복합 연산과 데이터 흐름을 하나의 구조로 압축해 정확도와 확장성을 동시에 확보한다. 셋째, 스코프 기반 메트릭 추출은 설계 설명성을 크게 향상시켜, 설계자와 비전문가 모두가 결과를 직관적으로 이해하도록 돕는다. 마지막으로, Archx의 프로그래밍 인터페이스는 DSL 수준의 간결함을 유지하면서도, 복잡한 제약 조건과 다중 목표 최적화를 지원한다.

댓글 및 학술 토론

Loading comments...

의견 남기기