하이퍼볼릭 그래프 신경망, 언제 진짜 필요할까

초록

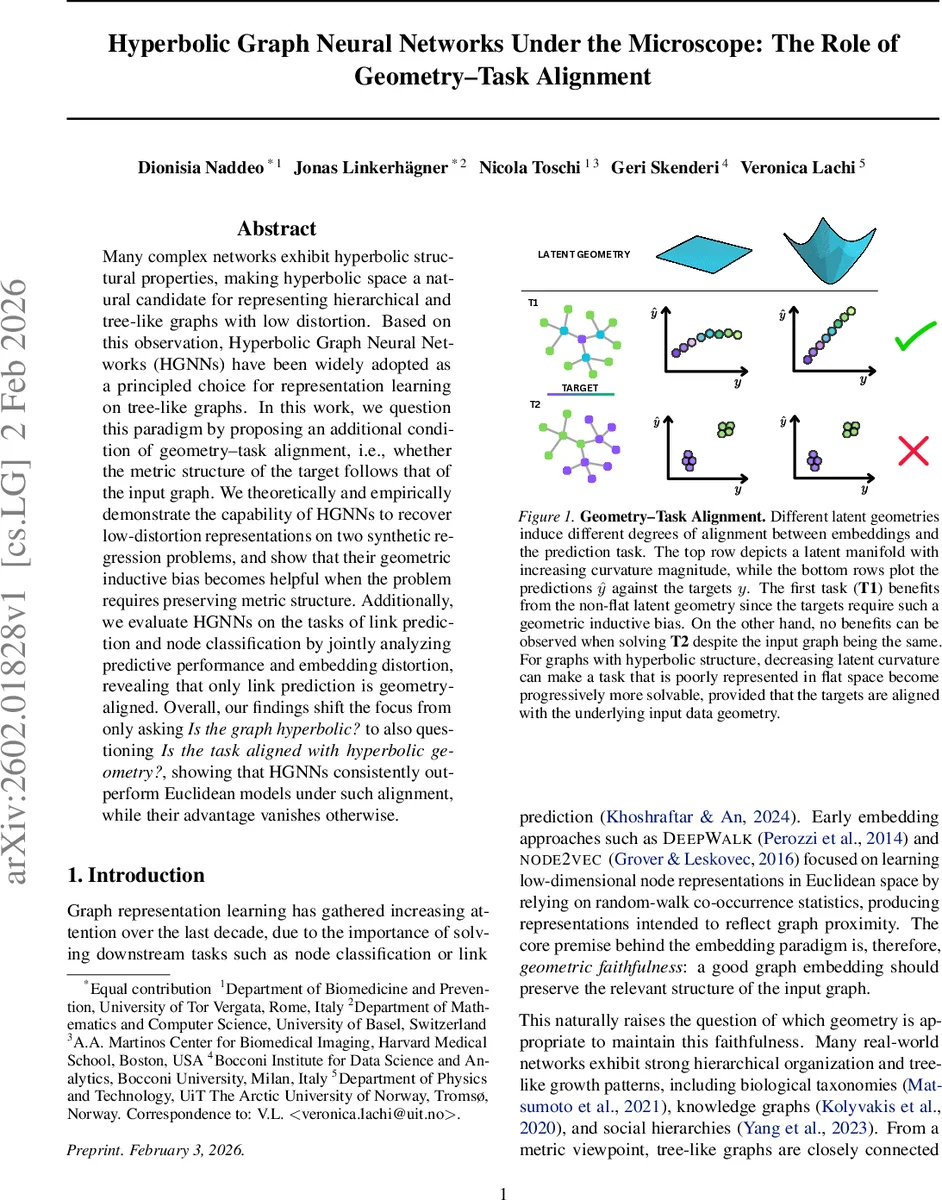

본 논문은 하이퍼볼릭 그래프 신경망(HGNN)이 입력 그래프의 하이퍼볼릭 구조만으로는 충분하지 않으며, 다운스트림 작업이 그래프의 메트릭 구조와 정렬되는 경우에만 성능 이점을 제공한다는 ‘기하‑작업 정렬(geometry‑task alignment)’ 개념을 제시한다. 합성 트리·격자 그래프에서 거리 예측(PDP) 과제를 통해 HGNN이 저왜곡 임베딩을 학습함을 보였으며, 실제 링크 예측에서는 정렬이 존재해 유리하지만 노드 분류에서는 이점이 사라진다.

상세 분석

이 논문은 기존 “그래프가 하이퍼볼릭이면 HGNN을 써라”는 직관을 비판하고, 두 번째 조건인 ‘기하‑작업 정렬(geometry‑task alignment)’을 도입한다. 즉, 목표 변수(예: 링크 존재 여부, 노드 레이블)가 입력 그래프의 메트릭 구조와 얼마나 일치하는가가 핵심이다. 저자는 먼저 임베딩 왜곡(distortion)의 수학적 정의를 제시한다. 왜곡 δ(h)=δ_c·δ_e≥1 은 그래프의 최단경로 거리 d_G와 임베딩 공간의 측지 거리 d_M 사이의 양쪽 Lipschitz 상수를 의미한다. δ=1이면 완전 등거리(또는 스케일링) 임베딩이며, 트리와 같은 계층 구조는 하이퍼볼릭 공간에서 임의의 낮은 차원으로도 δ≈1에 가깝게 임베딩될 수 있다(Sarkar, 2011).

이를 검증하기 위해 저자는 Pairwise Distance Prediction(PDP)이라는 합성 회귀 과제를 설계한다. 그래프의 모든 노드 쌍 (i,j)에 대해 실제 최단경로 거리 D_ij를 레이블로 사용하고, 임베딩 z_i=h_ϕ(x_i)에서 측지 거리 ˆd_ij를 구한 뒤 선형 디코더 a·ˆd_ij+b 로 D_ij를 예측한다. 손실은 stress loss = Σ

댓글 및 학술 토론

Loading comments...

의견 남기기