제피러스 차세대 클라우드 게이트웨이: DPU와 ASIC 융합의 혁신

초록

제피러스는 고성능 Tofino 스위치 ASIC과 프로그래머블 DPU를 하나의 P4 파이프라인으로 통합하고, 계층형 공동 오프로드(HLCO) 구조를 통해 99% 이상의 패킷을 하드웨어에서 처리한다. 이를 통해 petabit 규모 트래픽을 저지연·고처리량으로 지원하면서 전력·비용 효율성을 크게 개선한다.

상세 분석

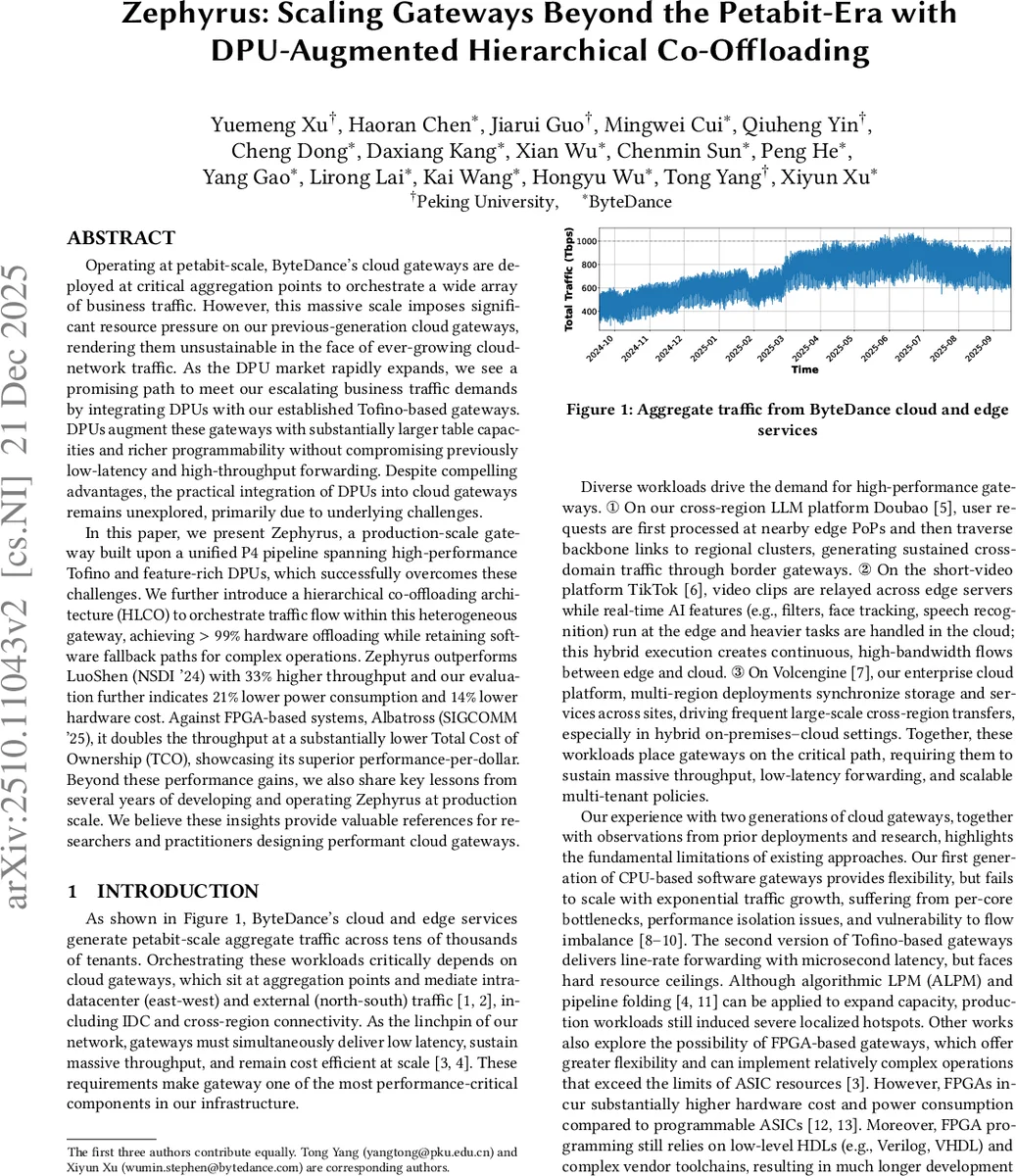

본 논문은 초대형 클라우드 환경에서 발생하는 petabit 수준의 트래픽을 처리하기 위한 새로운 게이트웨이 아키텍처를 제시한다. 기존 세대의 소프트웨어 전용 게이트웨이는 CPU 코어당 병목과 흐름 불균형으로 확장성이 제한됐으며, ASIC 기반 Tofino 게이트웨이는 라인 레이트 포워딩과 마이크로초 수준의 지연을 제공하지만 온칩 SRAM 용량이 급격히 소진돼 대규모 라우팅·정책 테이블을 수용하지 못한다는 한계가 있었다. 이러한 문제를 해결하기 위해 저자는 DPU를 도입한다. DPU는 대용량 메모리와 풍부한 프로그래머블 로직을 제공해 VM‑to‑NC 매핑과 같은 대규모 테이블을 ASIC 외부에 오프로드한다. 핵심 설계 포인트는 (1) ASIC과 DPU가 동일한 P4 언어를 사용하도록 통합 파이프라인을 정의하고, (2) 메타데이터 포맷을 최소화하면서도 양쪽 장치 간 상태 동기화를 보장하는 버전 기반 흐름 업데이트 메커니즘을 구현한 것이다.

계층형 공동 오프로드(HLCO) 구조는 전통적인 fast‑path/slow‑path 모델을 세 단계로 확장한다. 최상위 fast‑path는 Tofino ASIC에서 초당 수 테라비트 수준의 패킷을 처리하고, 중간 단계인 DPU는 복잡도는 낮지만 테이블 크기와 정책 유연성이 요구되는 작업을 담당한다. 최하위 소프트웨어 레이어는 드물게 발생하는 복합 로직이나 상태ful 처리를 수행한다. 이 설계는 99 % 이상의 패킷을 하드웨어에서 처리하도록 보장하면서, 남은 1 %에 대해서는 소프트웨어가 안전하게 폴백할 수 있게 한다.

성능 평가에서는 기존 최첨단 ASIC 기반 게이트웨이 LuoShen(NSDI ‘24) 대비 33 % 높은 처리량을 달성했으며, 전력 소모는 21 % 절감, 2U 섀시당 하드웨어 비용은 14 % 감소했다. 또한 FPGA 기반 Albatross(SIGCOMM ‘25)와 비교했을 때 처리량은 2배, TCO는 현저히 낮아 비용 대비 성능이 크게 우수함을 입증한다. 운영 경험을 통해 얻은 교훈으로는 (① 하드웨어 업그레이드 시 서비스 연속성을 위한 단계적 롤아웃, ② DPU와 ASIC 간의 정확한 리소스 매핑을 위한 자동화 툴 체인, ③ 장애 복구를 위한 메타데이터 버전 관리) 등을 제시한다.

결과적으로 제피러스는 대규모 멀티테넌트 클라우드 환경에서 요구되는 저지연·고처리량·대용량 테이블·비용 효율성을 모두 만족시키는 실용적인 솔루션으로, 향후 클라우드 네트워크 인프라의 표준 설계 패러다임을 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기