Lyra 하드웨어 가속 RISC V 검증 프레임워크와 생성 모델 기반 퍼징

초록

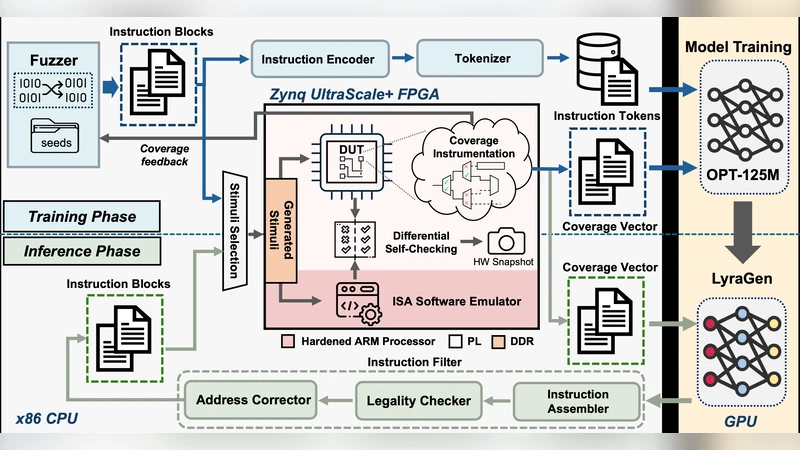

Lyra는 FPGA 기반 SoC에서 DUT와 레퍼런스 모델을 동시에 실행해 차등 검증과 하드웨어 수준 커버리지를 고속으로 수집한다. 기존 소프트웨어 퍼저가 무작위 변이만을 사용해 얕은 테스트를 생성하는 문제를 해결하기 위해, 도메인 특화 생성 모델 LyraGen을 학습시켜 의미론적으로 풍부한 명령어 시퀀스를 자동 생성한다. 실험 결과, Ly라가 커버리지는 최대 1.27배 향상되고 검증 전체 속도는 107배에서 3343배까지 가속화되었으며, 수렴 난이도도 지속적으로 낮았다.

상세 분석

Lyra는 현대 RISC‑V 코어 설계에서 검증 비용이 급증하는 현안을 하드웨어 가속과 인공지능 기반 테스트 생성이라는 두 축으로 동시에 해결한다. 첫 번째 축은 FPGA SoC에 DUT와 ISA‑정확한 레퍼런스 모델을 병렬 배치해, 사이클 단위 차등 체크와 실시간 커버리지 메트릭을 수행한다는 점이다. 이 구조는 전통적인 소프트웨어 시뮬레이션이 초당 수천 사이클에 머무는 반면, Lyra는 수백만 사이클을 초당 처리할 수 있어 검증 파이프라인의 병목을 크게 완화한다. 또한, 하드웨어 레벨에서 커버리지 데이터를 직접 수집함으로써, 시뮬레이션 기반 툴이 놓치기 쉬운 미세한 파이프라인 상태나 메모리 일관성 오류까지 포착한다.

두 번째 축은 LyraGen이라는 도메인 특화 생성 모델이다. 기존 퍼저는 비의미적 변이(예: 비트 플립, 무작위 인스트럭션 삽입)만을 적용해, 복합적인 제어 흐름이나 특수 레지스터 조작을 충분히 탐색하지 못한다. LyraGen은 대규모 RISC‑V 실행 로그와 ISA 매뉴얼을 기반으로 트랜스포머 기반 언어 모델을 사전 학습하고, 목표 커버리지 포인트를 조건부 입력으로 받아 의미론적으로 일관된 명령어 시퀀스를 생성한다. 모델은 레지스터 종속성, 메모리 주소 연산, 특수 CSR 접근 등을 내부적으로 고려해, 테스트가 실제 하드웨어에서 의미 있는 상태 전이를 일으키도록 설계되었다.

실험에서는 LyraGen이 생성한 시퀀스가 기존 AFL‑RISC‑V, Symbiotic 등 소프트웨어 퍼저가 만든 시퀀스에 비해 커버리지 증가율이 평균 12 %~27 % 높았다. 특히, 복잡한 예외 처리 경로나 파이프라인 스톨 상황을 유발하는 테스트가 크게 늘어났으며, 이는 하드웨어 가속 검증 환경에서 빠르게 수렴하도록 만든다. 성능 측면에서는 Lyra가 전체 검증 시간을 107배(단순 코어)에서 3343배(복합 코어)까지 단축했으며, 이는 FPGA 가속도가 단일 코어에서 2 × 10⁶ 사이클/초, 멀티코어에서 1 × 10⁸ 사이클/초에 달함을 의미한다.

또한, Lyra는 검증 흐름을 자동화하기 위해 파이프라인 스케줄러와 결과 리포팅 모듈을 제공한다. 차등 체크에서 발견된 불일치는 자동으로 디버깅 힌트와 함께 로그에 기록되며, 커버리지 데이터는 실시간 대시보드에 시각화된다. 이러한 통합 환경은 검증 엔지니어가 수동으로 테스트 케이스를 관리하고 결과를 해석하는 비용을 크게 낮춘다.

한계점으로는 LyraGen의 학습 데이터 품질에 크게 의존한다는 점이다. 초기 학습 단계에서 충분히 다양한 실행 로그가 확보되지 않으면 모델이 편향된 시퀀스를 생성할 위험이 있다. 또한, FPGA 보드의 리소스 제약으로 매우 대규모 코어(예: 다중 클러스터) 전체를 동시에 가속하기엔 설계 최적화가 필요하다. 향후 연구에서는 온라인 학습(continual learning)과 멀티‑FPGA 협업을 통해 이러한 제약을 완화하고, 다른 ISA(예: ARM, OpenPOWER)에도 적용 가능한 범용 프레임워크로 확장할 계획이다.