아날로그 IC 배치에 라우팅 인식 강화

초록

**

본 논문은 아날로그 집적 회로의 배치 단계에 라우팅 친화성을 내재화하기 위해 강화학습과 관계 그래프 신경망(R‑GCN)을 결합한 자동 배치 엔진을 제안한다. 고해상도 격자, 핀 정보 정밀 활용, 동적 라우팅 자원 할당, HPWL 중심 보상 설계 등을 추가하여 기존 학습 기반 방법 대비 배치 면적·데드 스페이스·와이어 길이·라우팅 성공률을 크게 향상시켰으며, A* 기반 라우팅 엔진을 통해 실험적으로 73 % 이상의 라우팅 실패율 감소와 13 % 이상의 데드 스페이스 감소를 입증하였다.

**

상세 분석

**

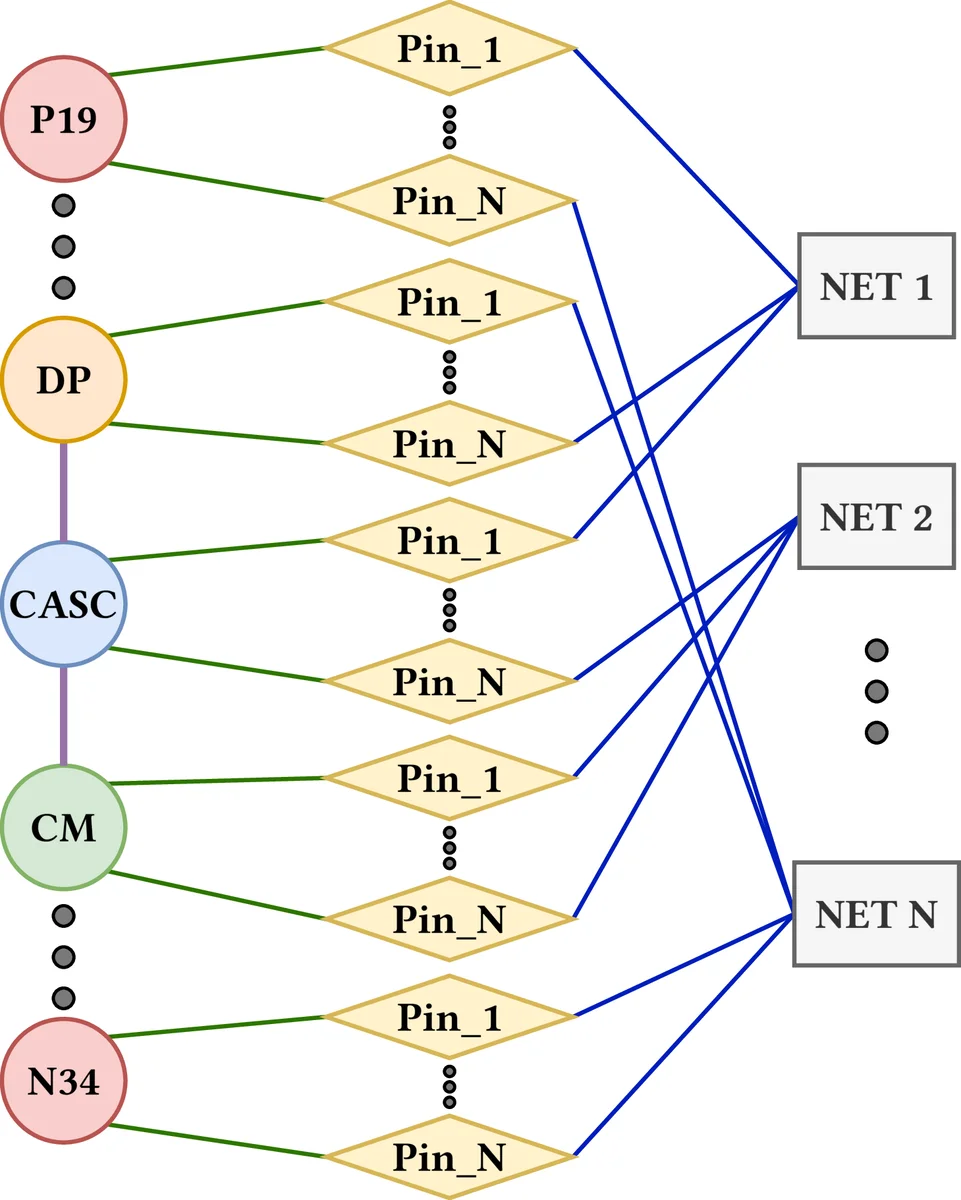

이 연구는 아날로그 IC 설계에서 배치와 라우팅이 상호 의존적인 문제라는 점을 명확히 인식하고, 기존 메타휴리스틱이나 단순 CNN 기반 배치 방법이 라우팅 단계에서 발생하는 병목을 충분히 고려하지 못한다는 한계를 짚어낸다. 이를 극복하기 위해 저자는 세 가지 핵심 기술을 도입한다. 첫째, 격자 해상도를 32×32에서 256×256으로 확대함으로써 디바이스 배치의 미세 조정이 가능하도록 하였으며, 이와 동시에 U‑Net 구조를 채택한 정책 네트워크를 설계해 고해상도 마스크 이미지와 R‑GCN 임베딩을 효과적으로 융합하였다. 둘째, 회로 네트리스트를 그래프 형태로 표현하고, 노드에 핀 정보를 포함시켜 R‑GCN이 전기적 연결성뿐 아니라 핀 위치·수량까지 학습하도록 함으로써 HPWL(반주변선 길이) 추정 정확도를 크게 높였다. 셋째, 동적 라우팅 자원(DRR) 할당 메커니즘을 도입해 각 블록 주변에 핀 수와 방향에 기반한 패딩을 자동으로 부여함으로써 라우팅 혼잡을 사전에 완화하고 DRC 위반을 방지한다. 보상 함수는 최종 단계에서 면적, HPWL, 목표 종횡비의 가중합을 사용하고, α≫β≫γ 형태의 사전 순위 가중치를 적용해 HPWL 감소를 최우선 목표로 삼았다. 또한, 제약 위반 시 -1000의 큰 페널티를 부여해 설계 규칙을 엄격히 준수하도록 유도한다. 학습은 Proximal Policy Optimization(PPO)과 커리큘럼 학습을 결합해 작은 회로부터 점진적으로 복잡한 회로까지 확장했으며, 130 nm 상용 기술 노드 기반 10개의 다양한 아날로그 블록을 데이터셋으로 사용했다. 실험에서는 제안된 라우팅‑인식 배치가 기존 R‑GCN 기반 0‑shot 및 1000‑shot 모델에 비해 데드 스페이스를 13.8 % 감소, 와이어 길이를 40.6 % 감소, 라우팅 성공률을 73.4 % 향상시켰다. 특히, 가장 복잡한 24‑블록 딜레이 라인 회로에서 라우팅 성공률이 76 %에 달했으며, 평균 라우팅 시간은 48.7 초로 실용적인 수준을 보였다. 이러한 결과는 라우팅 친화적인 배치가 아날로그 설계 자동화에서 실질적인 가치가 있음을 입증한다.

**

댓글 및 학술 토론

Loading comments...

의견 남기기