전용 프리필·디코드 하드웨어로 LLM 추론 효율 극대화

LLM 추론은 연산 중심의 프리필 단계와 메모리 중심의 디코드 단계로 구분된다. 기존 GPU/TPU는 두 단계 모두에 과잉 자원을 할당해 비용과 전력을 낭비한다. 본 논문은 프리필 전용 칩과 디코드 전용 칩을 각각 설계한 SPAD 아키텍처를 제안한다. 프리필 칩은 큰 systolic array와 저비용 GDDR 메모리를, 디코드 칩은 높은 메모리 대역폭을

초록

LLM 추론은 연산 중심의 프리필 단계와 메모리 중심의 디코드 단계로 구분된다. 기존 GPU/TPU는 두 단계 모두에 과잉 자원을 할당해 비용과 전력을 낭비한다. 본 논문은 프리필 전용 칩과 디코드 전용 칩을 각각 설계한 SPAD 아키텍처를 제안한다. 프리필 칩은 큰 systolic array와 저비용 GDDR 메모리를, 디코드 칩은 높은 메모리 대역폭을 유지하되 연산량을 축소한다. 시뮬레이션 결과, 프리필 칩은 H100 대비 8 % 빠른 성능을 52 % 낮은 비용으로 제공하고, 디코드 칩은 97 % 성능을 28 % 낮은 TDP로 구현한다. 전체 시스템에서는 하드웨어 비용을 19‑41 % 절감하고 전력 소모를 2‑17 % 감소시키면서 동일한 서비스 수준을 유지한다. 모델·워크로드 변화에도 두 칩을 교차 배치해 11‑43 % 비용 절감 효과를 유지한다.

상세 요약

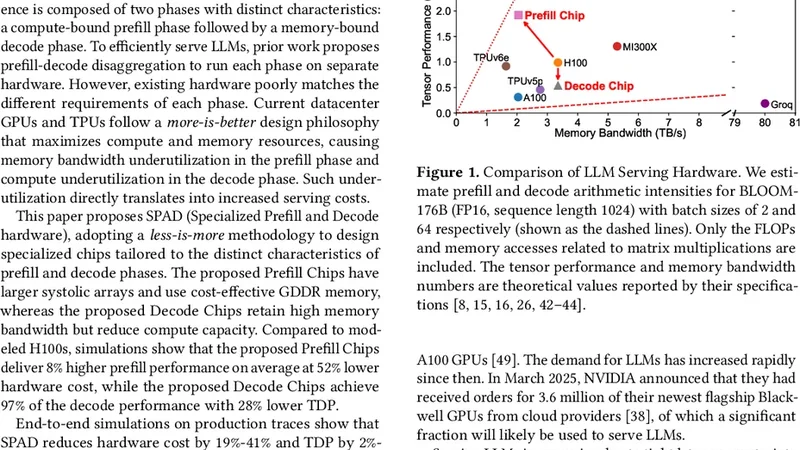

LLM 추론 파이프라인을 프리필(prefill)과 디코드(decode) 두 단계로 명확히 구분한 점은 기존 연구와 차별화되는 핵심 인사이트이다. 프리필 단계는 입력 토큰 전체를 한 번에 처리하면서 대규모 행렬 곱셈을 수행하므로 연산 집약도가 높고, 메모리 대역폭 요구가 상대적으로 낮다. 반면 디코드 단계는 한 토큰씩 순차적으로 생성하면서 매 스텝마다 이전 토큰들의 키‑값을 조회해야 하므로 메모리 대역폭이 병목이 된다. 기존 데이터센터 GPU와 TPU는 “more‑is‑better” 설계 철학에 따라 연산 유닛과 메모리 대역폭을 모두 최대화했지만, 이는 각각의 단계에서 자원 비효율을 초래한다. 프리필에서는 과도한 메모리 대역폭이 활용되지 않아 비용이 불필요하게 상승하고, 디코드에서는 연산 유닛이 충분히 활용되지 않아 전력 소모가 비효율적이다.

SPAD는 이러한 비대칭성을 해결하기 위해 “less‑is‑more” 접근을 채택한다. 프리필 전용 칩(Prefill Chip)은 대형 systolic array를 확대해 행렬 곱셈 처리량을 극대화하고, 비용 효율이 높은 GDDR 메모리를 채택해 메모리 대역폭을 적절히 유지한다. 이는 프리필 단계에서 연산량을 빠르게 소화하면서도 메모리 비용을 크게 절감한다는 장점을 만든다. 디코드 전용 칩(Decode Chip)은 메모리 대역폭을 유지하면서 연산 코어 수를 감소시켜 TDP를 낮춘다. 메모리 대역폭이 디코드 단계의 핵심이므로, 연산 유닛을 축소해도 성능 저하가 최소화된다.

시뮬레이션 결과는 설계 선택의 타당성을 뒷받침한다. 모델링된 H100 대비 프리필 칩은 평균 8 % 높은 처리량을 제공하면서 하드웨어 비용을 52 % 절감한다. 디코드 칩은 97 % 수준의 성능을 유지하면서 전력 소모(TDP)를 28 % 낮춘다. 전체 클러스터 수준에서는 실제 서비스 트레이스를 이용한 엔드‑투‑엔드 시뮬레이션을 통해 비용 절감 효과가 19‑41 %에 달하고, 전력 절감은 2‑17 %에 이른다. 특히 모델 크기와 워크로드가 변해도 두 종류의 칩을 서로 교체 배치할 수 있어 11‑43 %의 추가 비용 절감이 가능하다는 점은 SPAD의 장기적인 경제성을 강조한다.

이 논문은 하드웨어 설계에서 “one‑size‑fits‑all” 접근이 비효율적일 수 있음을 실증적으로 보여준다. LLM 추론처럼 단계별 특성이 뚜렷한 워크로드에 대해 맞춤형 가속기를 도입하면 비용·전력 효율을 크게 개선할 수 있다. 또한, SPAD는 기존 데이터센터 인프라와 호환성을 유지하면서도 전용 칩을 추가 배치하는 형태이므로, 단계적 도입이 가능하고 기존 투자 대비 높은 ROI를 기대할 수 있다. 향후 연구에서는 프리필·디코드 외에도 정교화된 라인(예: 리트리벌, 라인 파인 튜닝) 단계에 대한 전용 가속기 설계와, 칩 간 고속 인터커넥트 최적화가 추가된다면 더욱 포괄적인 LLM 서비스 효율화를 달성할 수 있을 것으로 보인다.

📜 논문 원문 (영문)

🚀 1TB 저장소에서 고화질 레이아웃을 불러오는 중입니다...