칩렛 퀘이크: 온칩 디지털 임피던스 센싱으로 칩렛·인터포저 보안 검증

초록

본 논문은 FPGA 기반 칩렛에 디지털 주파수 스위핑 회로와 TDC 기반 전압 센서를 결합한 “ChipletQuake” 프레임워크를 제안한다. 공유 전원 전달 네트워크(PDN)의 임피던스를 실시간으로 측정함으로써 인접 칩렛이나 인터포저에 발생한 물리적 변조(하드웨어 트로잔 삽입, 인터포저 손상 등)를 비접촉 방식으로 탐지한다. 실험 결과, 미세한 수동 회로 삽입까지도 높은 정확도로 검출함을 보인다.

상세 분석

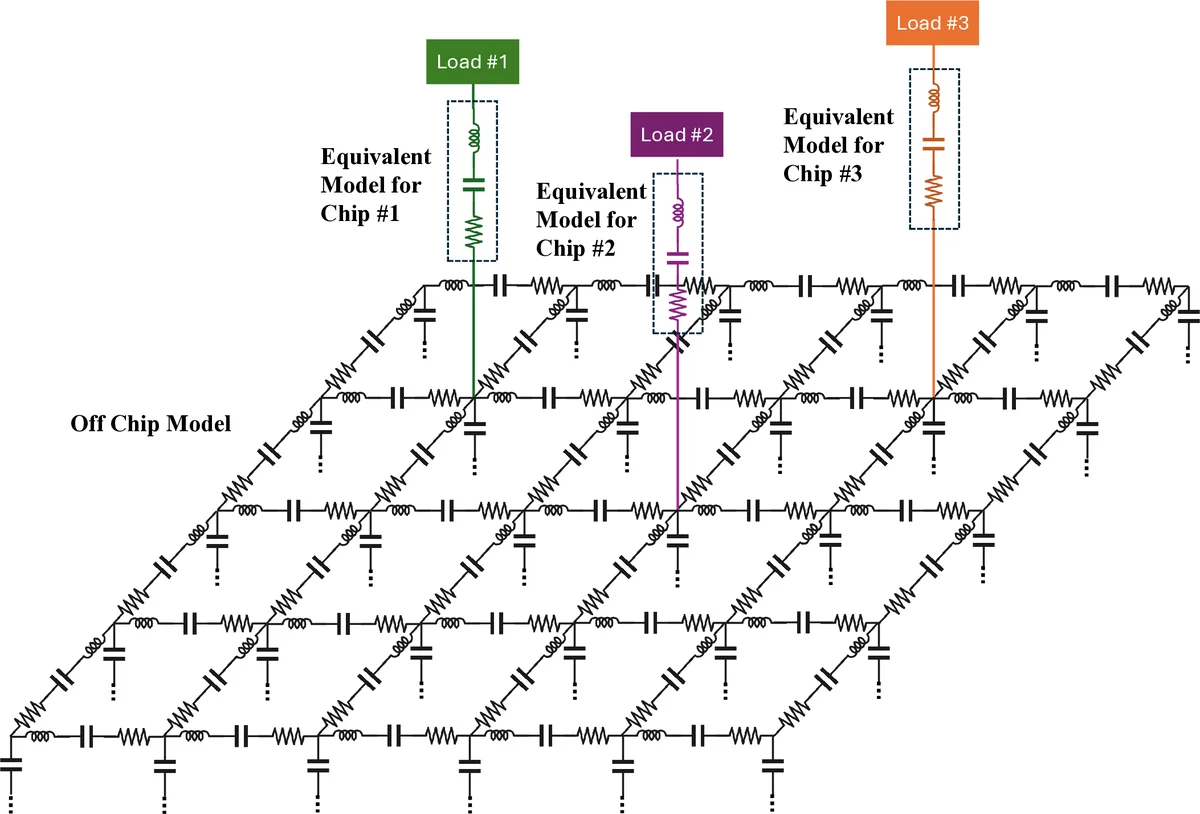

ChipletQuake은 기존의 링오실레이터·TDC 기반 전압 변동 감지 방식이 갖는 저정밀·고노이즈 문제를 극복하기 위해, 전원망 전체에 걸친 임피던스 스펙트럼을 디지털적으로 추출한다는 점에서 혁신적이다. 논문은 PDN을 저주파에서는 VRM·오프칩 캐패시터가, 고주파에서는 패키지·인터포저·µ‑범프와 같은 미세 구조가 지배하는 복합 RLC 네트워크로 모델링하고, 각 주파수 대역에서 임피던스 변화가 물리적 변조에 민감함을 실험적으로 입증한다.

핵심 구현은 두 가지 모듈로 구성된다. 첫 번째는 ‘액추에이터 어레이’로, FPGA 내부에 배치된 전류 소모 회로를 선택된 주파수대로 구동해 PDN에 의도적인 전류 파형을 주입한다. 두 번째는 동일 칩렛에 배치된 2D 메쉬형 TDC 센서 어레이로, 액추에이터가 만든 전압 변동을 피코초 수준의 시간 지연으로 변환해 디지털 값으로 기록한다. 이때 사용된 TDC는 기존 설계와 동일하게 캐리 체인 기반 지연 라인을 활용하였으며, 캘리브레이션 단계에서 온칩 온도·공정 변동을 보정한다.

검증 흐름은 챌린지‑응답 방식으로 설계되었다. 검증 키(Kver)는 무작위로 선택된 액추에이터·센서 ID와 주파수 집합을 포함하며, 이를 기반으로 ‘골든 모델’ 임피던스 서명을 사전에 저장한다. 런타임에 동일한 키로 재측정한 서명이 골든 모델과 일정 임계값을 초과하면 변조가 의심된 것으로 판단한다. 이 과정은 전용 메모리 없이도 실시간으로 수행 가능하도록 설계돼, 제한된 FPGA 리소스 환경에서도 적용 가능하다.

보안 측면에서 ChipletQuake은 물리적 변조를 전기적 특성(임피던스)으로 변환함으로써, 전통적인 신호 기반 인증이 불가능한 상황에서도 검증을 수행한다. 특히, 수동형 하드웨어 트로잔(전력 소모가 거의 없거나 동작이 비활성화된 회로)까지도 전력망에 미세한 정전용량·인덕턴스 변화를 일으키므로, 기존 전압·전류 모니터링 방식보다 높은 탐지 감도를 제공한다.

한계점으로는 고주파 측정 시 신호 무결성을 유지하기 위한 고속 샘플링 회로가 필요하고, 대규모 멀티칩 시스템에서는 액추에이터·센서 배치 최적화가 추가 연구 과제로 남는다. 또한, 악의적인 공격자가 골든 모델을 역추적해 동일한 임피던스 변화를 모방할 가능성도 존재한다는 점에서, 머신러닝 기반 이상 탐지와 결합한 다중 인증 메커니즘이 필요하다.

전반적으로 ChipletQuake은 디지털 설계만으로 물리적 보안 검증을 구현한다는 점에서 2.5‑D/3‑D 패키징 시대의 새로운 신뢰 모델을 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기