프로그래머블 하드웨어 기반 페이지랭크 가속기 설계

초록

본 논문은 AI와 데이터 집약형 작업을 위해 설계된 재구성 가능한 하드웨어 가속기를 제안한다. 메시지 기반의 최소 명령어 집합과 동적 프로그래밍 방식을 통해 페이지랭크 알고리즘을 5,000노드 단백질 네트워크에 대해 100회 반복을 213.6 ms 내에 수행한다.

상세 분석

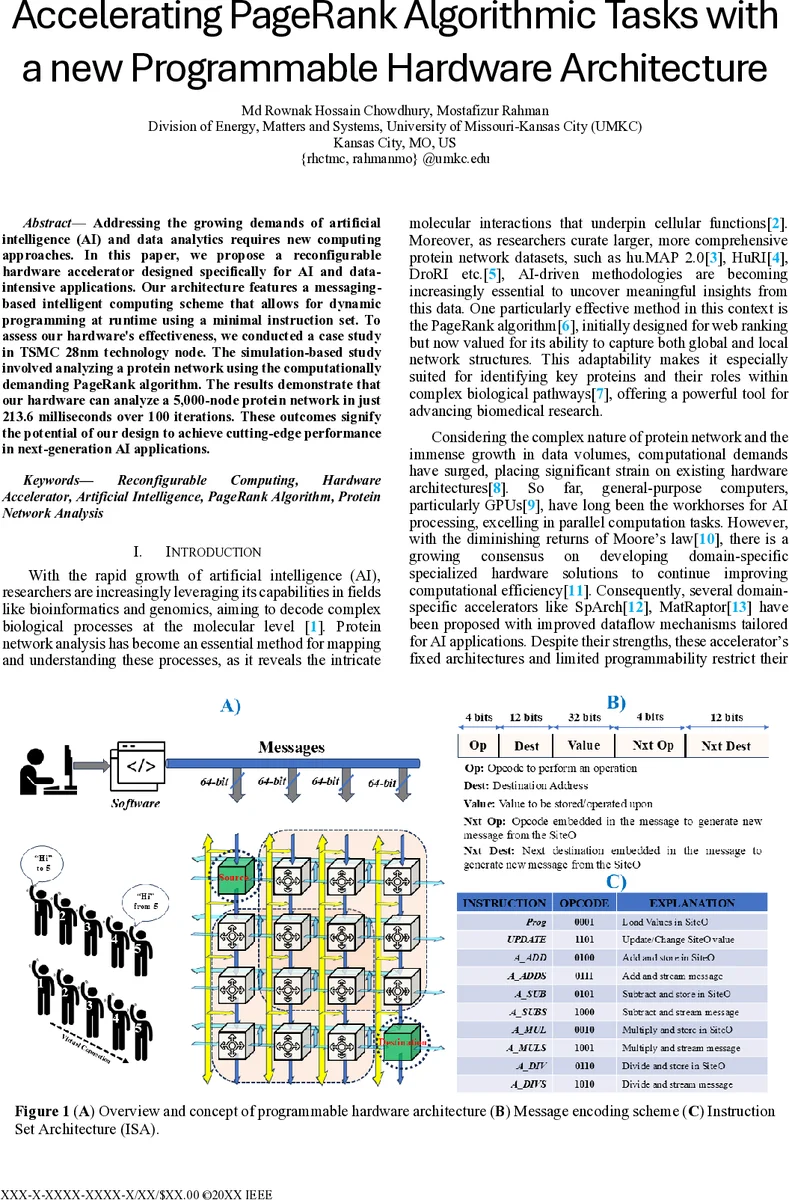

이 연구는 기존 CGRA와 FPGA가 갖는 설계 복잡성·런타임 재구성 한계를 극복하고자, “메시지 기반 프로그래머블 하드웨어”라는 새로운 아키텍처 패러다임을 도입한다. 핵심 아이디어는 데이터와 명령을 하나의 메시지에 캡슐화하고, 각 연산 유닛(PE)이 메시지의 목적지 주소와 opcode를 해석해 자동으로 라우팅·연산을 수행하도록 하는 것이다. 이를 위해 10개의 초소형 ISA를 정의했으며, 그 중 ‘Prog’ 명령은 데이터 로딩, 나머지 9개는 부동소수점 사칙연산 및 업데이트에 특화돼 있다.

아키텍처는 4×4(예시) 격자형 배열로 구성되며, 행·열 기반의 가상 링크를 통해 임의의 유닛 간에 메시지를 전달한다. 메시지 인코딩은 64비트 구조로, 상위 4비트는 opcode, 다음 12비트는 목적지 주소, 나머지는 피연산값을 담는다. 이러한 설계는 별도의 명령 메모리와 데이터 메모리를 통합함으로써 NoC 오버헤드를 크게 감소시키고, 라우팅 복잡성을 최소화한다.

특히 행렬‑벡터 곱 연산을 위한 전용 흐름을 제시한다. 행렬 A(N×M)는 행 단위로 “ hopping ” 방식으로 유닛에 분산되고, 벡터 B는 수직 버스를 통해 전송된다. 곱셈은 각 유닛에서 동시에 수행되며, 결과는 수평 버스를 이용해 집계·덧셈 후 최종 출력으로 오프로드한다. 시간 단계는 N+3으로, N은 행 수이며 열·벡터 크기에 독립적이다. 이는 전통적인 메모리·연산 분리 구조에 비해 대폭 낮은 지연을 제공한다.

페이지랭크 적용 사례에서는 네트워크 규모 N과 반복 횟수 n에 대해 전체 시간 단계가 n·(N+6)으로 모델링된다. 200 MHz 클럭, 4,096개의 유닛을 활용해 5,000노드·100회 반복을 213.6 ms에 처리했으며, 이는 동일 조건의 GPU나 CPU 대비 수십 배의 속도 향상을 의미한다. 전력 소모는 유닛당 4.1 mW(28 nm)로, 고밀도 설계에도 에너지 효율성을 유지한다.

이 논문의 의의는 (1) 최소 명령어 집합으로 복잡한 연산 흐름을 구현, (2) 런타임에 메시지만 교환하면 하드웨어 구성을 자유롭게 재프로그래밍 가능, (3) 행렬‑벡터 연산을 하드웨어 수준에서 파이프라인화해 데이터 규모에 선형적으로 확장 가능한 성능을 제공한다는 점이다. 다만, 현재 설계는 16유닛(4×4) 규모의 시뮬레이션에 머물러 있어 대규모 실리콘 구현 시 라우팅 충돌·버스 병목 현상이 어떻게 나타날지는 추가 검증이 필요하다. 또한, ISA가 부동소수점 연산에 국한돼 있어 정수 기반 AI 워크로드나 비선형 연산(예: 활성화 함수)에는 별도 확장이 요구된다. 전반적으로 메시지 기반 프로그래머블 하드웨어는 AI 전용 ASIC과 범용 가속기 사이의 중간 지점으로서, 설계 주기 단축과 비용 효율성을 동시에 달성할 수 있는 유망한 접근법이라 평가한다.

댓글 및 학술 토론

Loading comments...

의견 남기기