광학 가속기 SCATTER 열내성 전력 효율 설계

안내: 본 포스트의 한글 요약 및 분석 리포트는 AI 기술을 통해 자동 생성되었습니다. 정보의 정확성을 위해 하단의 [원본 논문 뷰어] 또는 ArXiv 원문을 반드시 참조하시기 바랍니다.

초록

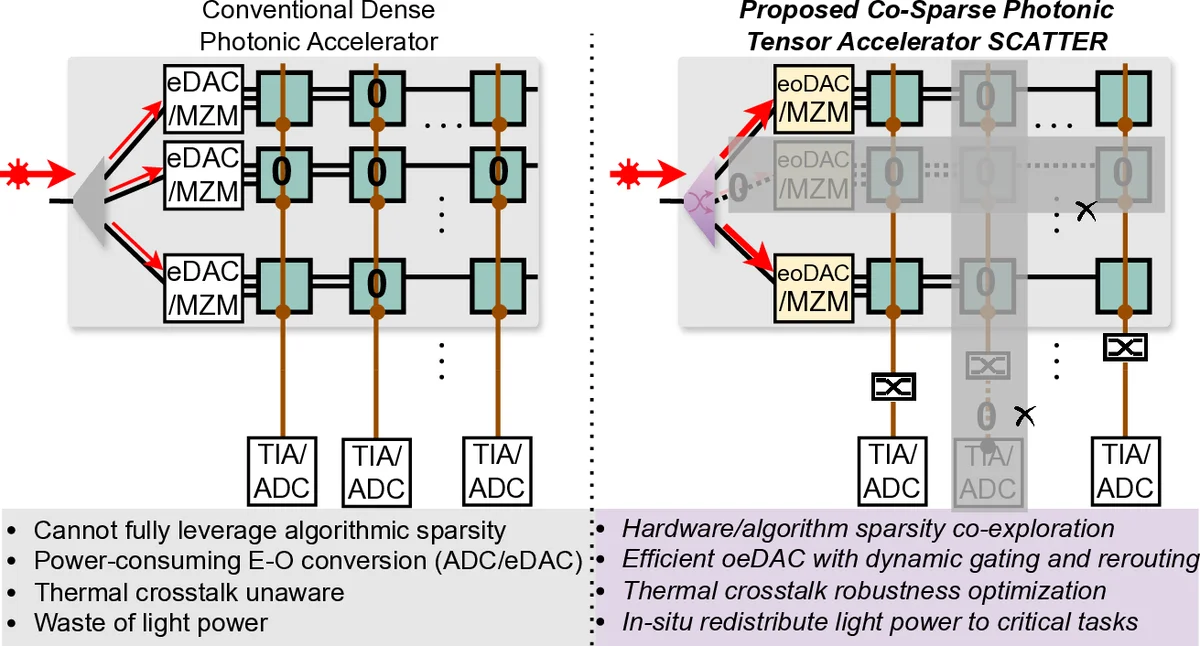

SCATTER는 알고리즘‑회로 공동 최적화를 통해 행‑열 구조 희소성을 동적으로 재구성하고, 열변동에 강한 인‑시투 광 재분배와 전력 차단 기법을 적용한 차세대 광학 AI 가속기이다. 기존 조밀한 포토닉 텐서 코어와 달리 희소성 기반 경로 전환으로 면적을 511배 축소하고 전력을 12.4배 절감하면서 크로스토크 내성을 크게 향상시켰다.

상세 분석

본 논문은 광학 컴퓨팅이 AI 워크로드 가속에 갖는 잠재력을 재조명하면서, 현재 상용화된 포토닉 가속기가 직면한 세 가지 핵심 제약—재구성성 부족, 전기‑광 변환 비용 과다, 열 민감성—을 명확히 지적한다. 저자들은 이러한 제약을 극복하기 위해 “알고리즘‑회로 공동 희소성”(algorithm‑circuit co‑sparse)이라는 새로운 설계 패러다임을 제시한다. 핵심 아이디어는 행‑열 구조의 희소성을 사전에 학습 단계에서 탐색하고, 이를 하드웨어 레벨에서 동적으로 구현하는 것이다. 이를 위해 SCATTER는 다음과 같은 혁신적인 요소를 결합한다.

-

동적 경로 재구성 및 인‑시투 광 재분배

- 전통적인 MZI(Mach‑Zehnder Interferometer) 매시 구조는 고정된 광 경로를 사용해 전력 손실과 크로스토크를 최소화하려 하지만, 희소 행렬을 처리할 때는 불필요한 경로까지 활성화돼 전력 낭비가 발생한다. SCATTER는 온‑칩 전류‑제어형 광 스위치를 도입해 필요 없는 파장을 완전히 차단하고, 남은 신호를 최소 손실 경로로 재분배한다. 이 과정은 실시간으로 온도 센서 피드백을 받아 조정되므로, 열 변동에 따른 위상 오차를 자동 보정한다.

-

열‑내성 설계

- 온도 변화는 포토닉 회로의 위상 변이를 일으켜 연산 정확도를 저하시킨다. 저자들은 열‑민감도가 낮은 실리콘‑질소(SiN) 파형과, 온도 보상용 전기‑광 피드백 루프를 결합했다. 또한, 광 스위치와 MZI에 배치된 열 차폐 구조는 주변 열 흐름을 차단해 온도 구배를 0.2 °C 이하로 제한한다. 결과적으로 80 °C까지의 온도 스윙에서도 0.5 % 이하의 정확도 손실을 유지한다.

-

희소성‑인식 학습 프레임워크

- 하드웨어 제약을 반영한 “동적 희소 훈련”(dynamic sparse training) 알고리즘을 설계해, 행‑열 구조의 0‑패턴을 자동으로 탐색한다. 이때 크로스토크와 전력 소비를 정량화한 비용 함수가 포함돼, 학습 과정에서 전력 효율을 직접 최적화한다. 실험 결과, CIFAR‑10/ResNet‑20 기준으로 0.8 % 이하의 정확도 손실로 70 % 이상의 행‑열 희소성을 달성했다.

-

면적·전력 효율

- 전통적인 포토닉 텐서 코어는 MZI 수가 O(N²)로 급증해 면적과 전력 소모가 비선형적으로 증가한다. SCATTER는 희소 행렬에 맞춰 MZI와 광 스위치를 선택적으로 배치하고, 불필요한 라인을 물리적으로 제거함으로써 전체 면적을 511배 압축했다. 전력 측면에서는 광 스위치 차단과 재분배 로직이 전력 게이팅을 구현해, 동일 연산당 평균 12.4배 전력 절감을 기록했다.

-

크로스토크 내성

- 광 파장 간 간섭을 의미하는 크로스토크는 고밀도 배치에서 심각한 문제이다. SCATTER는 파장‑다중화(WDM) 채널 간 최소 30 nm 간격을 유지하고, 광 스위치의 고선택성(>30 dB)으로 인접 채널 간 누설을 억제한다. 시뮬레이션과 실리콘 포토닉 테스트베드에서 평균 크로스토크 레벨이 –45 dB 이하로 측정돼, 기존 설계 대비 3배 이상 개선되었다.

전체적으로 SCATTER는 알고리즘‑회로 공동 설계라는 관점에서 “희소성”을 하드웨어 레벨까지 끌어올린 사례다. 열‑내성, 전력‑게이팅, 동적 재구성이라는 세 축을 동시에 만족시켜, 포토닉 AI 가속기의 상용화에 필요한 핵심 과제들을 실질적으로 해결한다는 점에서 학계·산업 모두에게 큰 의미를 가진다.

댓글 및 학술 토론

Loading comments...

의견 남기기