오픈소스 EDA 멀티밀리언 게이트 RV64 SoC 설계에 준비됐는가

초록

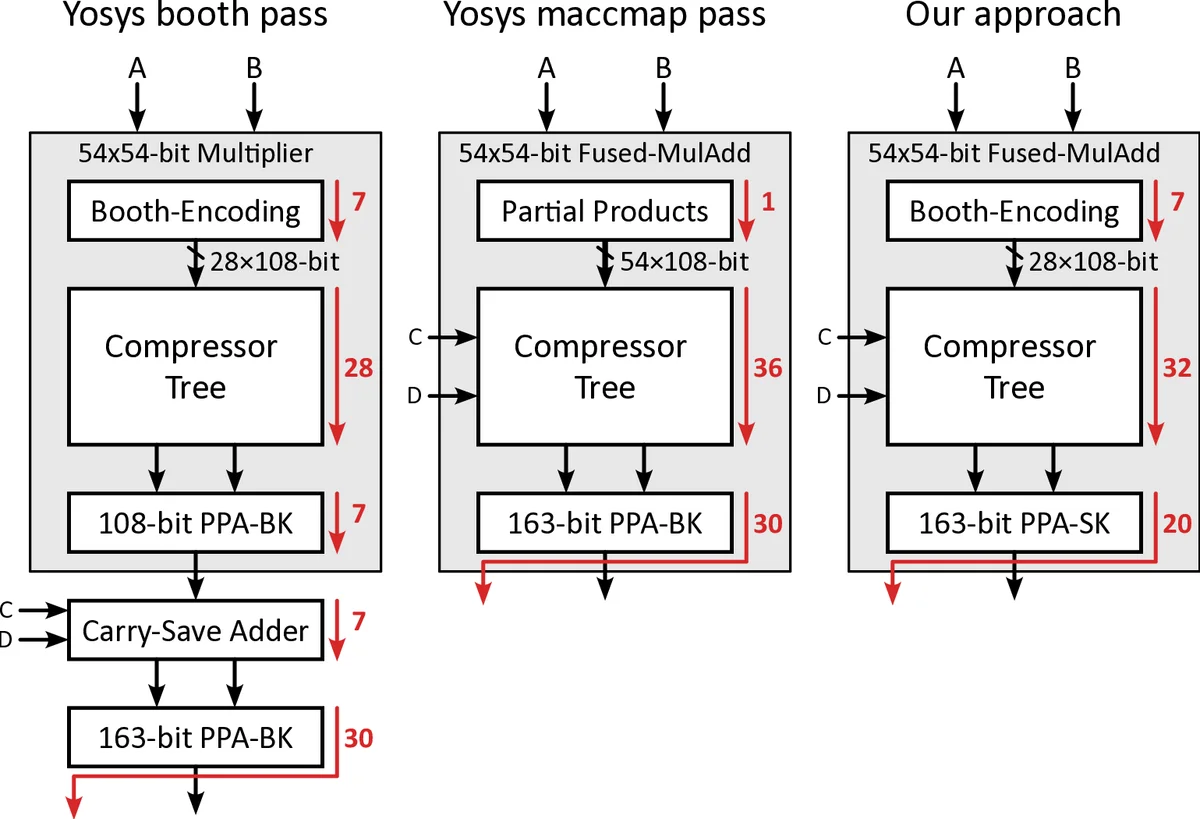

본 논문은 Yosys와 OpenROAD 기반 오픈소스 EDA 흐름을 확장·개선하여, 130 nm 공정에서 1.1 MGE 규모의 리눅스 부팅 RV64GC SoC인 Basilisk을 구현한 사례를 제시한다. 파트‑셀렉트 최적화, ABC Lazy‑Man Synthesis 도입, 손수 만든 산술 매크로 라이브러리 통합 등을 통해 논리 영역을 1.6배 축소하고 최고 77 MHz 동작 주파수를 달성했으며, 합성 시간·메모리 사용량도 크게 감소시켰다.

상세 분석

Basilisk 프로젝트는 오픈소스 EDA 툴 체인의 한계점을 정확히 짚어낸 뒤, 실질적인 QoR(품질‑결과) 향상을 위한 다중 레이어 최적화를 수행한다. 첫 번째 핵심은 SystemVerilog 기반의 Cheshire SoC RTL을 Yosys가 처리할 수 있는 순수 Verilog 형태로 변환하는 전처리 파이프라인이다. Bender‑Morty‑SVase‑SV2V 체인을 통해 복잡한 파라미터 전파와 다차원 배열을 일차원 팩킹으로 정리함으로써, 기존 Yosys가 지원하지 않던 고급 언어 구문을 손실 없이 보존한다.

두 번째 개선은 파트‑셀렉트 연산을 기존의 barrel‑shifter 구현에서 블록‑멀티플렉서 형태로 대체한 점이다. Yosys는 기본적으로 $shiftx 셀을 사용해 모든 셀렉트를 시프트 연산으로 매핑했으며, 이는 불필요한 논리와 다중 레벨을 초래한다. 연구팀은 스트라이드가 일정한 경우 이를 감지해 시프트 폭을 2의 거듭제곱으로 맞추고, 상수 전파를 통해 불필요한 비트들을 제거하는 최적화 패스를 새롭게 추가했다. 이 패스는 전체 설계에서 논리 영역을 약 22 % 절감하고, 최고 경로 레벨을 182 → 51 로 크게 단축시켰다.

세 번째는 ABC 내부 스크립트의 전면 개편이다. Lazy‑Man Synthesis(LMS) 기법을 도입해 6‑입력 레코드 라이브러리를 사전 생성하고, 설계 전체를 컷(cut) 단위로 분할해 최적 구조로 교체한다. Basilisk 특화 레코드를 추가함으로써 기존 ABC가 제공하던 최적화 수준을 넘어서는 논리 감소와 타이밍 향상을 얻었다. 결과적으로 합성 시간은 5.4 시간에서 2.2 시간으로 2.5배 가량 단축됐으며, 피크 메모리 사용량도 217 GB에서 75 GB 로 2.9배 감소하였다.

물리 설계 단계에서는 OpenROAD 흐름에 전력 그리드와 셀 배치 통합을 개선하였다. 전력망 최적화는 전압 강하와 IR‑드롭을 최소화하면서 면적 오버헤드를 억제했고, 배치 알고리즘은 매크로‑연산 라이브러리와의 연계성을 높여 고밀도 배치를 가능하게 했다. 최종 P&R 결과는 DRC 위반 없이 완료되었으며, 77 MHz(51 논리 레벨) 동작을 달성했다.

전체적으로 본 연구는 오픈소스 툴이 수백만 게이트 규모의 복잡한 SoC 설계에 충분히 경쟁력을 가질 수 있음을 실증한다. 특히, RTL 전처리, 합성 패스, ABC 최적화, 물리 설계 전반에 걸친 체계적 개선이 각각 독립적인 성능 향상을 제공함과 동시에 누적 효과를 만들어낸 점이 주목할 만하다. 이러한 접근은 향후 더 작은 공정(65 nm 이하)이나 고성능 애플리케이션에도 확장 가능성을 시사한다.

댓글 및 학술 토론

Loading comments...

의견 남기기