프리라우팅 타이밍 예측을 위한 순서 보존 파티션 기반 글로벌·로컬 학습 프레임워크

초록

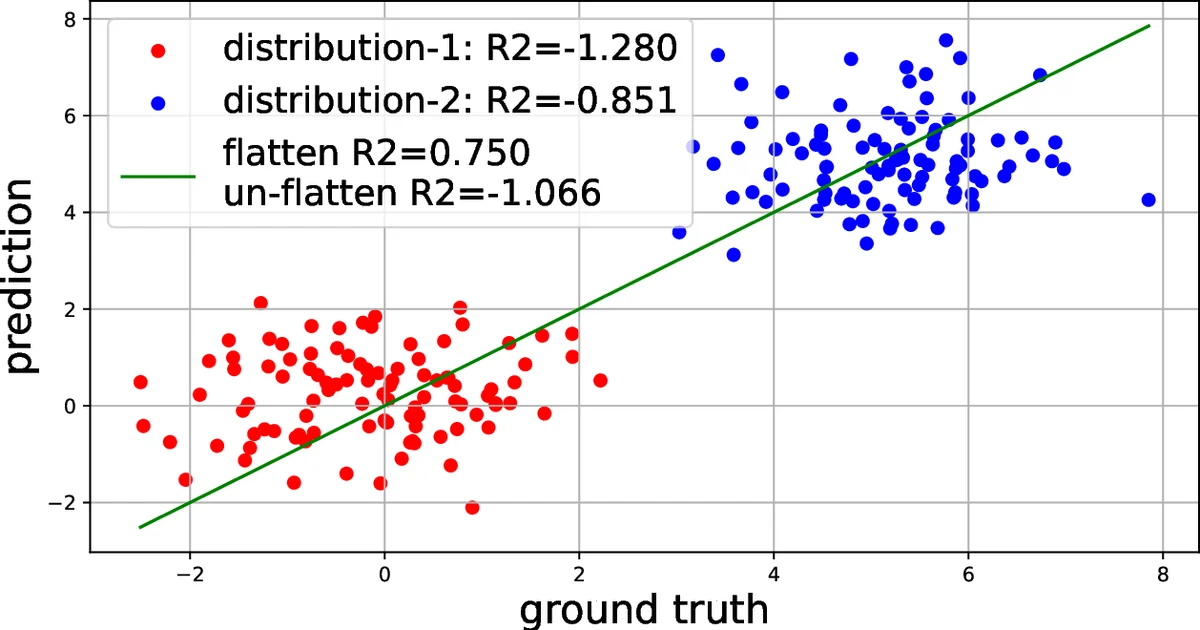

본 논문은 대규모 산업 회로에서 라우팅 없이 후보 셀 배치를 평가할 수 있는 프리라우팅 타이밍 예측 방법을 제안한다. 전체 회로를 그래프 자동인코더로 사전 학습해 전역 임베딩을 획득하고, 이를 토대로 토폴로지 정렬 순서에 맞는 GCN 메시지 전달 방식을 설계한다. 인접 핀 사이의 로컬 지연을 잔차 형태로 모델링하고, 셀 내부의 LUT 정보를 추출하기 위해 새로운 어텐션 메커니즘을 도입한다. 또한 메모리 사용량을 크게 낮추면서도 토폴로지 의존성을 유지하는 순서 보존 파티션 기법을 제안한다. 21개의 실제 회로 실험에서 슬랙 예측 R² 0.93을 달성, 기존 최고 0.59를 크게 앞선다.

상세 분석

본 연구는 프리라우팅 타이밍 예측의 핵심 난제인 신호 감쇠와 오류 누적을 두 단계 학습 구조로 해결한다. 첫 번째 단계인 글로벌 회로 사전 학습에서는 회로 넷리스트를 비지도 그래프 자동인코더(GAE)에 입력해 전체 회로의 구조적 특성을 압축한 전역 임베딩을 얻는다. 이 임베딩은 회로 내 노드(핀) 간의 장거리 상관관계를 포착하며, 이후 로컬 학습 단계에서 메시지 전달 순서를 결정하는 기준으로 활용된다. 두 번째 단계에서는 GCN 기반 메시지 전달을 기존의 이웃 집합 기반이 아닌, 사전 학습된 전역 임베딩에 의해 정의된 토폴로지 정렬 순서에 따라 수행한다. 정렬된 순서대로 각 노드의 상태를 업데이트하면서, 현재 노드와 바로 앞선 노드 사이의 지연을 잔차 형태로 모델링한다. 이는 긴 경로에서 발생하는 누적 오차를 단계별로 보정할 수 있게 해준다. 셀 내부의 LUT(lookup table) 정보를 효과적으로 추출하기 위해 제안된 어텐션 메커니즘은 각 셀의 입력 핀 집합에 가중치를 할당하고, 해당 가중치를 기반으로 셀 레벨의 비선형 변환을 수행한다. 이렇게 하면 전통적인 셀 모델링에서 놓치기 쉬운 미세한 전기적 특성을 학습할 수 있다. 대규모 회로의 메모리 요구를 완화하기 위해 도입된 순서 보존 파티션은 회로 그래프를 여러 파티션으로 나누되, 각 파티션 내에서는 토폴로지 순서를 유지한다. 파티션 간 경계에서는 최소한의 인터페이스 정보를 교환함으로써 전체 그래프의 의존성을 보존한다. 실험 결과는 21개의 실제 산업 회로에 대해 슬랙 예측 R² 0.93, 슬루 및 지연 예측에서도 기존 최첨단 방법 대비 20~30% 이상의 개선을 보여준다. 특히 파티션 기법을 적용했을 때 메모리 사용량이 60% 이상 감소하면서도 정확도 손실이 거의 없다는 점이 실용성을 크게 높인다.

댓글 및 학술 토론

Loading comments...

의견 남기기