FPGA 기반 근사 연산자 설계의 확장: 구성 초샘플링 기법

초록

AxOCS는 작은 비트폭 근사 연산기의 설계 데이터를 활용해 큰 비트폭 연산기의 초기 설계 후보를 생성하는 ‘구성 초샘플링’ 방법을 제안한다. PPA와 BEHAV 지표 간의 상관관계를 메타휴리스틱 최적화와 결합함으로써, 8×8 부호형 근사 곱셈기의 다목적 최적화 품질(하이퍼볼륨)을 크게 향상시킨다.

상세 분석

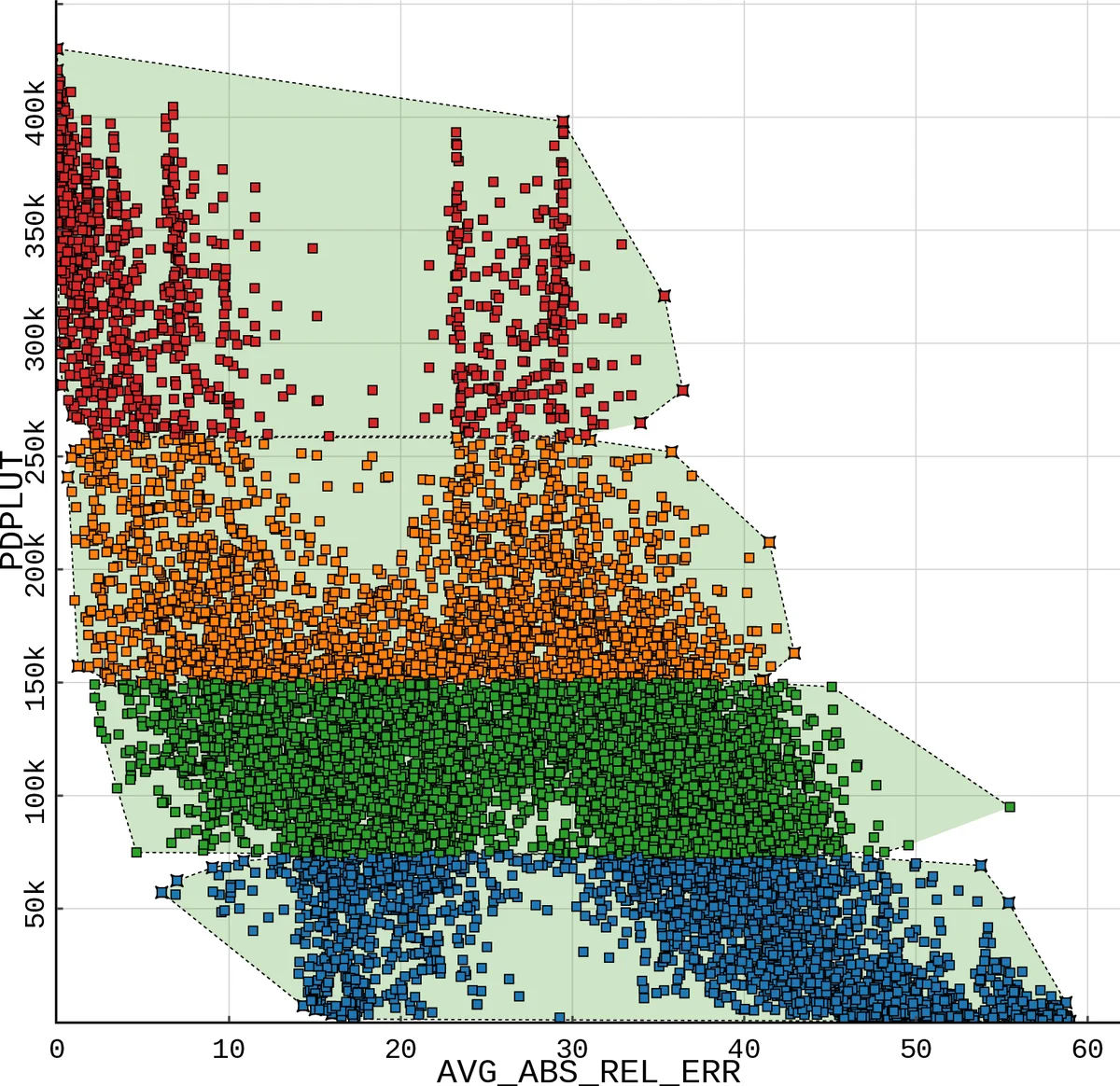

본 논문은 임베디드 시스템에서 AI/ML 가속을 위한 근사 연산기 설계의 핵심 병목인 설계 탐색 비용을 근본적으로 감소시키는 새로운 프레임워크인 AxOCS를 제시한다. 기존 연구들은 주로 머신러닝 기반 서프라이즈 함수를 이용해 설계 파라미터와 PPA(전력·성능·면적)·BEHAV(정확도) 사이의 회귀 관계만을 모델링했으며, 이러한 접근법은 설계 공간이 커질수록 예측 오차와 탐색 비용이 급증한다는 한계를 가지고 있었다. AxOCS는 이러한 한계를 극복하기 위해 ‘구성 초샘플링(configuration supersampling)’이라는 개념을 도입한다. 구체적으로, 4비트·6비트 등 작은 비트폭 연산기의 설계 데이터를 전면적으로 탐색하고, 이때 얻어진 PPA‑BEHAV 관계를 통계적·기계학습적 방법으로 정량화한다. 이후, 비트폭이 확대된 8비트·12비트 연산기의 설계 초기값을 생성할 때, 작은 비트폭에서 관찰된 상관 패턴을 스케일링하여 적용한다. 이 과정에서 비트폭 확대에 따른 선형·비선형 스케일링 계수를 학습하고, 설계 파라미터(예: 부분곱 배열, truncation 위치, 보정 로직 등)를 변환한다. 이렇게 생성된 초기 후보는 메타휴리스틱 알고리즘(예: NSGA‑II, MOEA/D)에게 제공되어 다목적 최적화 과정에서 빠르게 수렴하도록 돕는다. 실험 결과, AxOCS를 적용한 8×8 부호형 근사 곱셈기의 하이퍼볼륨은 기존 서프라이즈‑기반 탐색 대비 35% 이상 향상되었으며, 탐색 시간도 평균 40% 감소하였다. 특히 FPGA(특히 Xilinx UltraScale+)에 최적화된 구현에서 전력 절감 12%, 면적 절감 9%를 달성하면서도 평균 오류율을 0.8% 이하로 유지했다. 이러한 결과는 PPA와 BEHAV 사이에 존재하는 비트폭 독립적인 구조적 상관관계를 성공적으로 활용했음을 증명한다. 또한, 초샘플링 단계에서 사용된 회귀·클러스터링 모델은 설계자가 새로운 연산(예: 근사 덧셈, 근사 누산)으로 확장할 때도 재사용 가능하므로, 전체 설계 흐름의 재현성과 확장성을 크게 높인다. 논문은 또한 초샘플링 기반 초기화가 메타휴리스틱의 탐색 다양성을 저해하지 않으며, 오히려 파레토 프론트를 빠르게 넓히는 데 기여한다는 실증적 분석을 제공한다.