저전력 비터비 디코더 탐색을 위한 근사 가산기 활용

초록

본 논문은 Viterbi 디코더의 핵심 연산인 Add‑Compare‑Select Unit(ACSU)에 근사 가산기를 적용해 정확도·전력·면적 간 트레이드오프를 빠르게 탐색하는 프레임워크 Locate를 제안한다. 통신 시스템과 자연어 처리(NLP) 두 분야에 적용해, 평균 0.14% 이하의 정확도 손실로 면적 2123%·전력 2831% 절감을 달성하였다.

상세 분석

Locate 프레임워크는 Viterbi 디코더 설계 단계에서 가장 비용이 많이 드는 ACSU에 초점을 맞춘다. ACSU는 경로 메트릭을 계산하고, 비교·선택을 수행하는데, 이 과정에서 다수의 전가산기가 연속적으로 작동한다. 기존 설계에서는 정확성을 보장하기 위해 고속·정밀한 캐리룩어헤드 가산(CLA)을 사용하지만, 이는 면적과 전력 소모가 크게 증가한다. Locate는 다양한 근사 가산기(Approximate Adders, AA)를 라이브러리화하고, 각 AA의 오류 특성(오프셋, 평균 절대 오차 등)과 하드웨어 메트릭(게이트 수, 클럭 주기, 전력)을 사전 측정한다. 이후 설계 공간 탐색(DSE) 엔진이 목표 정확도(예: 비트 오류율, POS 태깅 정확도)와 전력·면적 제약을 입력받아, 가능한 AA 조합을 평가한다.

핵심 기법은 두 단계로 나뉜다. 첫 번째는 ‘정확도 모델링’ 단계로, 근사 가산기의 오류가 전체 Viterbi 경로 메트릭에 미치는 영향을 통계적 시뮬레이션을 통해 추정한다. 여기서는 메트릭 오차가 누적되면 경로 선택이 바뀔 가능성을 확률적으로 계산하고, 이를 기반으로 허용 가능한 오류 한계를 정의한다. 두 번째는 ‘하드웨어 평가’ 단계로, 선택된 AA를 실제 RTL에 삽입해 합성·배치 후 전력·면적을 측정한다. 이 두 단계는 자동화 파이프라인으로 연결돼, 수십 개의 AA 후보에 대해 수백 개의 설계 포인트를 빠르게 생성한다.

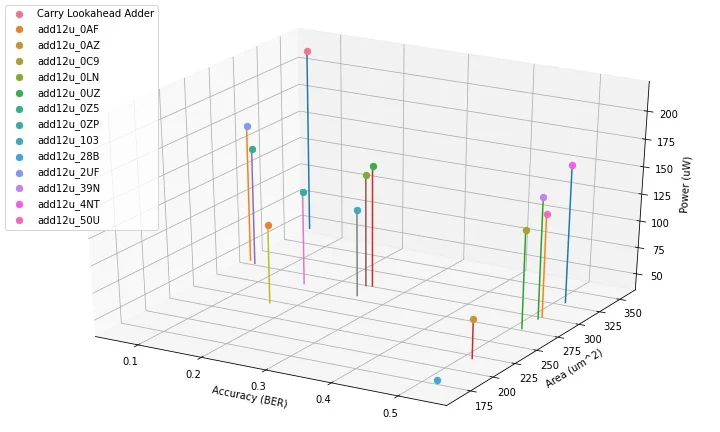

실험에서는 두 개의 대표 응용을 선정했다. 첫 번째는 16‑QAM, 64‑QAM, 256‑QAM 등 세 가지 변조 방식을 사용하는 디지털 통신 시스템이며, 두 번째는 영어 텍스트에 대한 품사 태깅(POS Tagger) 작업이다. 통신 시스템에서는 근사 가산기 중 하나를 ACSU에 적용했을 때, 평균 정확도 손실이 0.142%에 불과하면서 면적 21.5%와 전력 31.02%를 절감했다. NLP 실험에서는 15개의 AA 중 7개가 원본 CLA와 동일한 100% 정확도를 유지했으며, 평균 면적 22.75%·전력 28.79% 절감 효과를 보였다. 특히, 오류가 누적되기 쉬운 긴 시퀀스(예: 1024‑비트 트레일)에서도 일부 AA는 정확도 저하 없이 효율성을 크게 높였다.

Locate의 장점은 (1) 설계 초기 단계에서 빠른 DSE가 가능해 설계 주기가 단축된다, (2) 근사 가산기 라이브러리를 확장하면 새로운 공정이나 전력 제한에 맞춰 손쉽게 재탐색할 수 있다, (3) 기존 최적화 기법(전압 스케일링, 클럭 게이팅 등)과 병행 적용이 용이해 전체 시스템 효율을 극대화한다는 점이다. 한계점으로는 근사 가산기의 오류 모델링이 특정 데이터 패턴에 민감할 수 있어, 극한 환경(예: 저 SNR, 고 잡음)에서는 추가 검증이 필요하다는 점이다. 또한, 현재는 ACSU에만 적용했지만, Viterbi 디코더의 다른 블록(예: traceback unit)에도 근사 연산을 확대하면 더 큰 절감 효과를 기대할 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기