저장 장벽 나노자석을 이용한 이진 확률 신경망 설계의 실질적 과제

초록

저장 장벽이 낮은 나노자석(LBM)은 열잡음에 의해 자화가 무작위로 변동하여 이진 확률 신경망(BSN)의 하드웨어 가속에 적합하다. 그러나 제조 공정에서 발생하는 미세 결함이 자화 상관시간과 스핀 편극 고정 전류를 크게 변동시키므로, 실제 LBM을 이용한 BSN 설계는 높은 공정 제어와 수율 확보가 필수적이다.

상세 분석

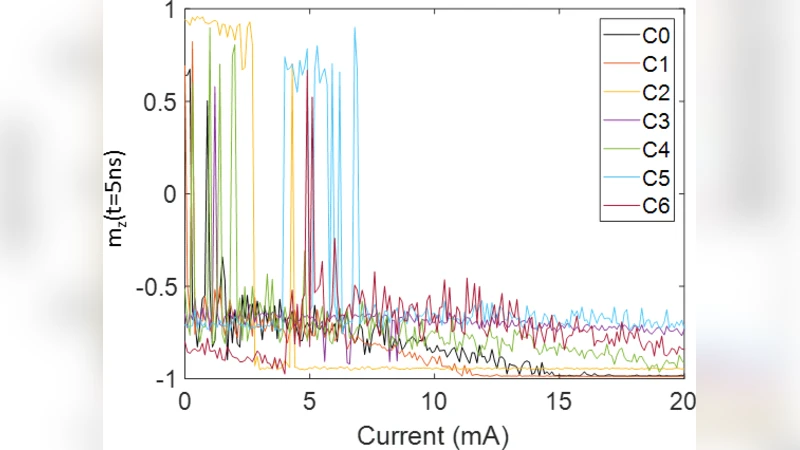

본 논문은 저장 장벽이 낮은 나노자석(LBM)이 열적 플럭투에 의해 자화가 빠르게 전이되는 특성을 이용해 이진 확률 신경망(BSN)의 랜덤 비트원을 구현한다는 기본 아이디어를 검토한다. BSN의 핵심 성능 지표는 (1) 자화 상관시간 τ_c, 즉 자화가 독립적인 샘플로 전환되는 평균 시간과 (2) 스핀‑편극 전류 I_p, 즉 외부 전류에 의해 원하는 방향으로 자화를 고정시키는 데 필요한 전류 크기로 정의된다. 이 두 파라미터는 이론적으로는 재료의 자기 이방성, 체적, 감쇠 상수, 온도 등에 의해 예측 가능하지만, 실제 제조 과정에서 발생하는 결함—예를 들어, 표면 거칠기, 비균일한 두께, 불완전한 산화층, 미세한 입자 포함—이 자기 에너지 장벽과 스핀 전송 효율을 비선형적으로 변조한다는 점을 저자들은 실험적 시뮬레이션과 통계적 모델링을 통해 입증한다. 특히, 결함이 1 nm 수준의 미세 변동이라도 자화 전이 확률 분포를 크게 왜곡시켜 τ_c가 수십 배에서 수천 배까지 변동하게 만든다. 동시에, 결함에 의해 스핀‑전달 토크 효율이 감소하면 동일한 고정 효과를 얻기 위해 필요한 I_p가 급격히 상승한다. 이러한 민감도는 설계 마진을 크게 축소시키며, 공정 변동을 허용하는 설계 공간이 사실상 사라짐을 의미한다. 논문은 또한 결함이 특정 방향성(예: 결정립 경계)과 연관될 경우, 자화의 비대칭성이 도입되어 BSN의 출력 확률이 0.5를 벗어나게 되고, 이는 학습 알고리즘의 수렴에 악영향을 미친다. 따라서 저자들은 (i) 결함 민감도를 정량화하는 파라미터(예: 결함 민감 계수 η)를 도입하고, (ii) 설계 단계에서 Monte‑Carlo 기반 공정 변동 시뮬레이션을 수행해 최소 수율 목표를 만족하는 설계 포인트를 탐색할 것을 제안한다. 마지막으로, 현재의 전자빔 리소그래피와 원자층 증착(ALD) 기술이 제공하는 공정 정밀도가 아직 요구되는 0.5 nm 이하의 변동을 보장하지 못한다는 점을 강조하며, 향후 초고정밀 나노패브리케이션 기술 개발이 BSN 실용화의 핵심 과제임을 결론짓는다.

댓글 및 학술 토론

Loading comments...

의견 남기기