다중소스 데이터 흐름 최적화를 위한 흐름 행렬과 보로노이 클러스터링 기반 NoC 설계

초록

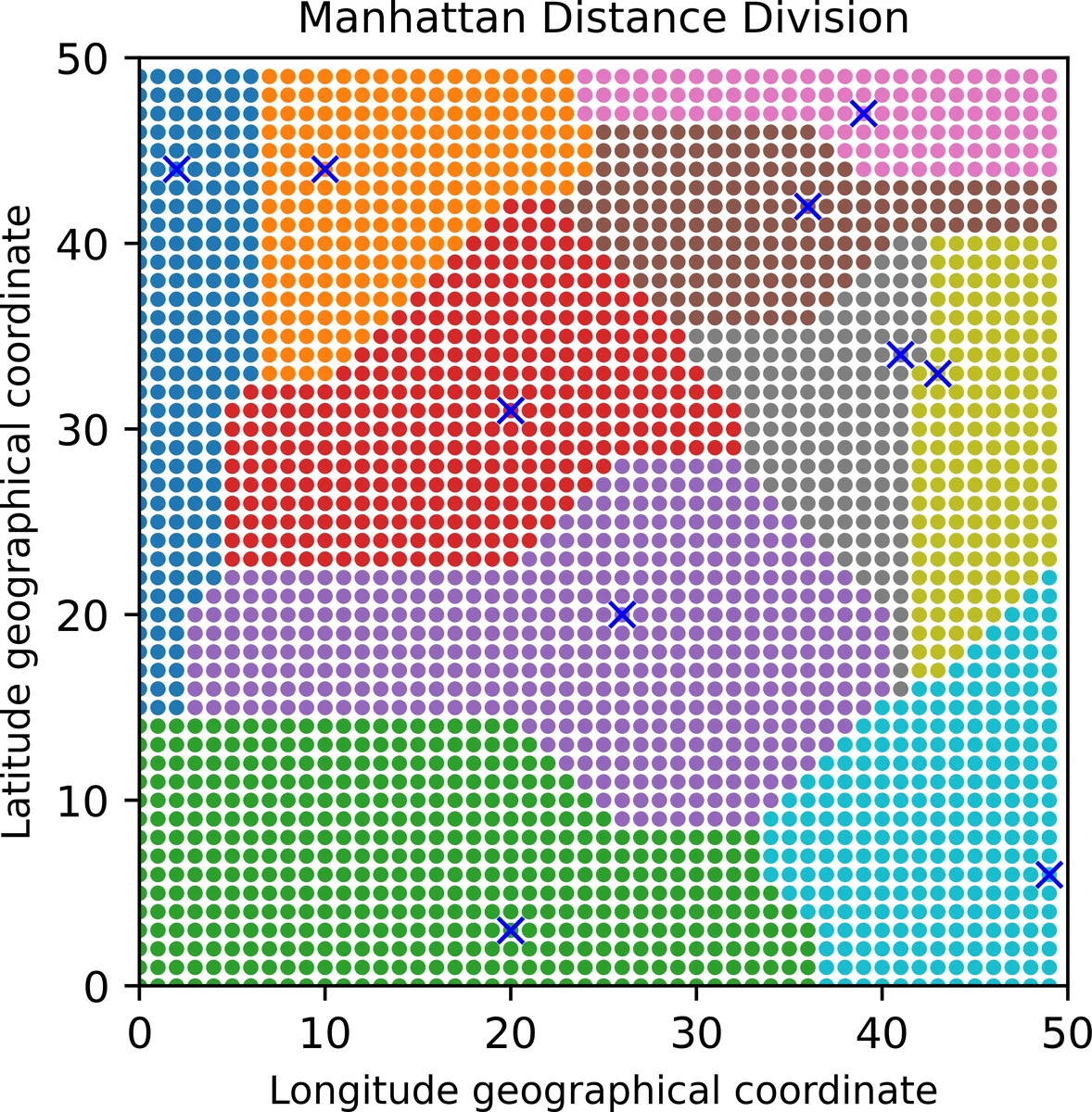

본 논문은 균등 분할 부하(divisible load) 이론을 바탕으로, 메쉬형 네트워크‑온‑칩(NOC)에서 다중 데이터 주입점이 존재할 때 최적의 부하 배분과 최소 makespan을 달성하는 새로운 수학적 도구인 “흐름 행렬(flow matrix)”을 제안한다. 보로노이 다이어그램을 이용해 프로세서들을 클러스터링하고, 각 클러스터 내부에서 흐름 행렬을 풀어 각 프로세서에 할당될 부하 비율을 구한다. 이후 클러스터 간 부하를 재조정해 전체 시스템의 속도 향상과 사용 코어 수 감소(≈30%)를 입증한다.

상세 분석

이 논문은 네트워크‑온‑칩(NOC) 설계에서 데이터 집약적 워크로드를 효율적으로 분산시키는 두 가지 핵심 아이디어를 결합한다. 첫 번째는 보로노이 다이어그램을 이용해 다중 주입점(source) 주변의 프로세서들을 지리적으로 가장 가까운 영역으로 구분, 즉 “클러스터”를 형성한다는 점이다. 보로노이 셀은 각 셀 내에서 통신 거리가 최소화되므로, 셀 내부의 부하 배분 문제를 단순화한다. 두 번째는 기존의 가분 부하(divisible load) 이론을 행렬 형태로 정리한 ‘흐름 행렬(flow matrix)’을 도입한 것이다. 흐름 행렬 A는 각 홉 거리별 프로세서 수와 통신‑계산 비율 σ(=z·T_cm / ω·T_cp)를 매개변수로 하여, 부하 비율 α⃗을 구하는 선형 시스템 A·α = b 를 만든다. 여기서 b는 전체 부하가 1임을 나타내는 단위 벡터이며, α₀는 루트(주입점) 프로세서에 할당되는 부하 비율, α_i는 i‑홉 거리 프로세서들의 부하 비율을 의미한다.

논문은 2×2 메쉬 예시를 통해 흐름 행렬을 직접 구성하고, 행렬식(det A)의 절댓값이 바로 속도 향상(speedup)과 α₀의 역수임을 증명한다. 일반적인 m×n 메쉬에 대해서는 첫 행에 “0‑홉, 1‑홉, …, D‑홉”에 해당하는 프로세서 수가 순서대로 배치되고, 하위 행들은 σ와 1을 교차시킨 형태로 채워진다. 이 구조는 대칭성과 균일성을 보장해 Gaussian elimination 혹은 LU 분해로 O(r³) 시간에 해를 구할 수 있게 한다(여기서 r은 행렬의 차수).

다중 소스 상황에서는 세 가지 모델을 제시한다. (I) 주입점들이 연결된 유도 서브그래프를 형성하는 경우, (II) 주입점들이 서로 연결되지 않은 경우, (III) 혼합형태. 각 모델에 대해 ‘Equivalence Processor Scheduling Algorithm(EPSA)’를 적용한다. EPSA는 먼저 모든 주입점을 하나의 가상 “대형 프로세서”로 합쳐 등가 처리 속도 ω_eq 를 정의하고, 전체 네트워크에 대한 D_i 값을 계산한 뒤 흐름 행렬을 구성한다. 이후 행렬식과 α⃗을 구해 각 프로세서에 할당될 부하 비율을 얻는다.

실험 결과는 σ ≤ 0.05(통신이 매우 빠른 경우)에서 전체 36코어가 모두 활용되어 약 36배의 속도 향상을 달성하고, σ ≈ 1(통신과 계산 속도가 동일)에서는 12코어만이 효과적으로 사용돼 약 12배의 속도 향상을 보인다. 또한, 클러스터 간 부하 재조정을 통해 전체 사용 코어 수를 평균 30% 절감하면서도 makespan은 동일하게 유지한다. 이는 NoC 설계 시 면적 절감과 전력 효율성을 동시에 확보할 수 있음을 의미한다.

이 논문이 제공하는 흐름 행렬은 메쉬뿐 아니라 토러스, 하이퍼큐브 등 다양한 토폴로지에도 적용 가능하며, 스위칭 프로토콜이 변해도 동일한 선형 시스템 형태를 유지한다는 점에서 확장성이 뛰어나다. 또한, 행렬식 기반의 속도 향상 예측은 설계 단계에서 빠른 성능 추정 도구로 활용될 수 있다. 다만, 반환 통신을 무시하고, 모든 프로세서와 링크가 동질적이라는 가정이 현실적인 NoC 환경에서는 제한 요인으로 작용할 수 있다. 향후 연구에서는 비동질성, 동적 부하 변동, 전력‑열 제약 등을 포함한 모델 확장이 필요하다.

댓글 및 학술 토론

Loading comments...

의견 남기기