가속기 수준 병렬성: 차세대 컴퓨팅의 핵심 전략

초록

이 논문은 모바일 SoC에서 이미 나타나고 있는 가속기 수준 병렬성(ALP)을 정의하고, 기존의 BLP·ILP·TLP·DLP와 차별화되는 새로운 병렬성 계층으로 제시한다. 현재 스마트폰에 탑재된 다양한 전용 가속기들이 동시에 동작하는 사례를 분석하고, 효율적인 가속기 선택·배치·메모리 공유·스케줄링을 위한 과학적 방법론이 아직 부재함을 강조한다. 향후 연구 과제로는 통합 프로그래밍 모델, 시스템‑레벨 최적화, 그리고 전반적인 하드웨어‑소프트웨어 공동 설계가 제시된다.

상세 분석

본 논문은 가속기 수준 병렬성(ALP)을 기존의 병렬성 계층에 추가함으로써, 현대 SoC 설계의 새로운 패러다임을 제시한다. BLP(비트 수준 병렬성)는 기본 연산을 동시에 수행하고, ILP(명령 수준 병렬성)는 파이프라인·슈퍼스칼라·분기 예측 등을 통해 순차 명령을 겹쳐 실행한다. TLP(스레드 수준 병렬성)는 다중 코어를 활용하며, DLP(데이터 수준 병렬성)는 SIMD·GPU‑SIMT와 같은 구조로 동일 연산을 다수 데이터에 적용한다. ALP은 이러한 하위 병렬성을 모두 포함하면서, 서로 다른 전용 가속기(DSP, ISP, NPU, GPU 등)가 동시에 작동하는 것을 의미한다.

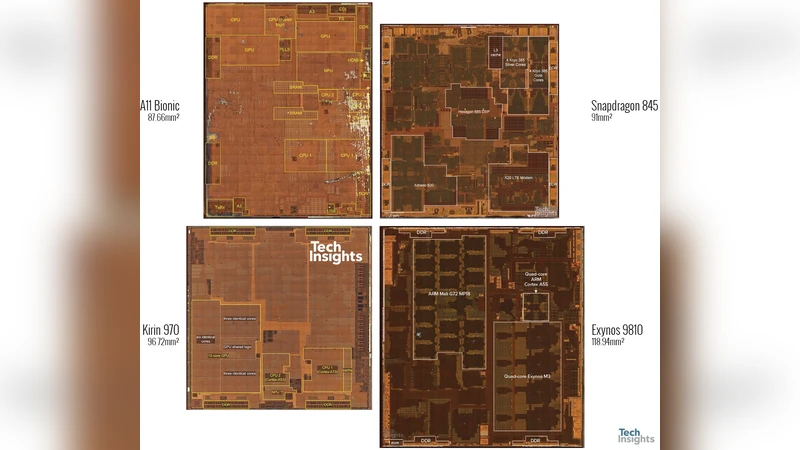

핵심 통찰은 다음과 같다. 첫째, 모바일 SoC에서 CPU가 차지하는 실리콘 면적이 50 % 이하이며, 나머지는 전용 가속기에 할당된다. 이는 전력·면적 효율성을 극대화하기 위한 설계 선택이며, ALP이 자연스럽게 발생한다는 점을 보여준다. 둘째, 현재 가속기들은 각각 독립된 소프트웨어 스택과 SDK를 갖고 있어, 개발자는 각 가속기에 맞는 전용 코드를 작성해야 한다. 이러한 ‘사일로’ 구조는 전체 시스템 차원의 최적화를 방해한다. 셋째, 논문은 ALP 활용을 위해 필요한 과학적 질문들을 제시한다. 예를 들어, 가속기 선택·크기 결정, 온‑칩 메모리의 사유·공유 정책, 데이터 전송 메커니즘(공유 메모리 vs. 큐), 그리고 배포 후 비선형 최적화 기반 스케줄링 여부 등이 있다.

또한, ALP은 기존의 이기종 스케줄링(CPU‑GPU)보다 복잡도가 높다. 가속기 수가 늘어나면 자원 충돌, 메모리 대역폭 경쟁, 전력 관리 문제가 급증한다. 따라서 전역 최적화를 위한 새로운 추상화 모델이 필요하다. 저자들은 GPU‑SIMT 모델을 참고하여, ALP 전용 ‘SIMT‑like’ 추상화를 제안한다. 이는 프로그래머가 전체 SoC를 하나의 일관된 실행 단위로 바라볼 수 있게 하며, 컴파일러·런타임이 내부 가속기 스케줄링을 자동화하도록 돕는다.

마지막으로, 논문은 ALP이 단순히 여러 가속기를 병렬로 배치하는 것이 아니라, 각 가속기의 내부 병렬성(BLP·ILP·TLP·DLP)을 활용해 전체 시스템 수준에서 글로벌 최적화를 달성해야 함을 강조한다. 이를 위해서는 하드웨어‑소프트웨어 공동 설계(Co‑design), 설계 공간 탐색을 지원하는 CAD 툴, 그리고 정량적 모델링이 필수적이다. 이러한 연구 방향이 정립될 경우, 스마트폰뿐 아니라 자율주행, AR/VR, 엣지·클라우드 서버까지 다양한 도메인에서 전력·성능 효율을 획기적으로 향상시킬 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기