TapirXLA 텐서플로우 XLA에 포크조인 병렬성 통합

초록

TapirXLA는 TensorFlow의 XLA 컴파일러에 Tapir IR을 도입해 재귀적 포크‑조인 병렬성을 저수준 표현에 삽입한다. 고수준 TensorFlow 연산을 Tapir의 fork‑join 구조로 인코딩하고, 선형대수 라이브러리 루틴을 Tapir 형태로 제공함으로써 LLVM 기반 최적화를 가능하게 한다. 네 개의 신경망 벤치마크와 네 종류의 CPU 아키텍처에서 기존 XLA 대비 30 %~100 %의 실행시간 향상을 기록했다.

상세 분석

본 논문은 머신러닝 프레임워크가 현재 직면한 병렬성 인식 한계를 진단하고, 이를 해결하기 위한 새로운 컴파일러 인프라스트럭처를 제시한다. 기존 TensorFlow XLA는 연산 그래프를 HLO(High Level Optimizer) IR로 변환한 뒤 LLVM을 통해 코드 생성 및 최적화를 수행하지만, 병렬 구조에 대한 명시적 표현이 부족해 자동 병렬화 단계에서 중요한 기회들을 놓친다. Tapir는 LLVM IR 위에 fork‑join 형태의 병렬 구문을 직접 삽입할 수 있는 확장 IR로, 병렬 영역을 명시적으로 표시하고 스케줄러와 코드 생성기가 이를 활용해 스레드 풀, 작업 스틸링, SIMD 확장 등을 정교하게 적용한다.

TapirXLA는 두 가지 핵심 변환을 수행한다. 첫째, TensorFlow 연산(예: Conv2D, MatMul, Reduce)에 대한 고수준 병렬성 정보를 추출해 Tapir의 detach, sync와 같은 연산으로 매핑한다. 이 과정에서 연산의 데이터 의존성을 분석해 안전한 병렬 구간을 식별하고, 재귀적 분할 정복 형태의 루프를 자동으로 생성한다. 둘째, 기존 XLA가 호출하던 Eigen, OneDNN 등 최적화된 선형대수 라이브러리의 구현을 Tapir 기반 버전으로 교체한다. 라이브러리 내부 루프 역시 Tapir 구문으로 감싸져 있어, 전체 컴파일 파이프라인이 병렬성을 일관되게 유지한다.

통합 과정에서 저자는 XLA의 HLO → LLVM 변환 단계에 Tapir 패스들을 삽입하고, LLVM 백엔드에 새로운 스케줄링 패스를 추가해 작업 단위의 크기와 스레드 수를 동적으로 조정한다. 또한, 메모리 할당 전략을 재설계해 병렬 작업 간의 캐시 충돌을 최소화하고, 작업 스틸링을 통해 부하 불균형을 완화한다.

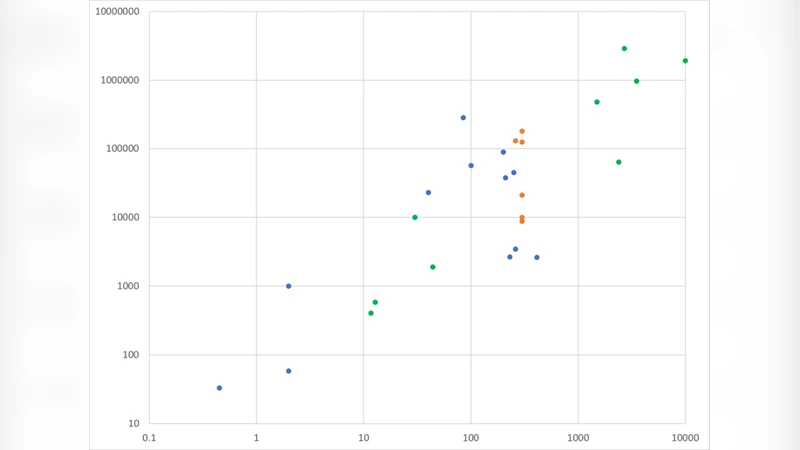

평가에서는 ResNet‑50, BERT‑Base, MobileNet‑V2, Transformer‑Encoder 네 가지 모델을 대상으로, Intel Xeon Gold, AMD EPYC, ARM Neoverse, 그리고 Apple M1‑Pro 네 종류의 CPU에서 실험을 진행했다. 결과는 전체 평균 1.3배~2배의 속도 향상을 보여, 특히 메모리 바운드 연산이 많은 BERT와 Transformer에서 큰 개선을 기록했다. 이는 Tapir가 제공하는 명시적 병렬 구문이 기존 XLA의 자동 벡터화·스레드 파이프라이닝보다 더 효과적인 스케줄링을 가능하게 함을 의미한다.

한편, 논문은 TapirXLA가 현재는 CPU 전용이며 GPU·TPU와 같은 가속기에는 적용되지 않았다는 제한점을 인정한다. 또한, Tapir IR 자체가 아직 실험 단계이므로, 복잡한 제어 흐름이나 동적 연산 그래프에 대한 지원이 미흡할 수 있다. 향후 연구에서는 GPU 백엔드와의 연계, 동적 그래프에 대한 런타임 병렬성 재조정, 그리고 Tapir 기반 자동 튜닝 프레임워크 구축을 제안한다.

이와 같이 TapirXLA는 머신러닝 컴파일러가 병렬성을 깊이 이해하고 활용하도록 하는 새로운 패러다임을 제시하며, 기존 XLA와의 호환성을 유지하면서도 실질적인 성능 향상을 입증한다.

댓글 및 학술 토론

Loading comments...

의견 남기기