Gemmini 전체 스택 통합으로 딥러닝 아키텍처 체계적 평가

초록

Gemmini는 오픈소스 전체 스택 DNN 가속기 생성기이다. 유연한 하드웨어 템플릿, 다계층 소프트웨어 스택, 그리고 RISC‑V 기반 SoC 통합을 제공해 설계‑프로그램‑시스템 전반을 동시에 탐색한다. 실제 ASIC 구현에서 CPU 대비 최대 2 670배 가속을 보이며, 가상 메모리, TLB 관리, 메모리 파티셔닝 등 시스템 수준 최적화도 지원한다.

상세 분석

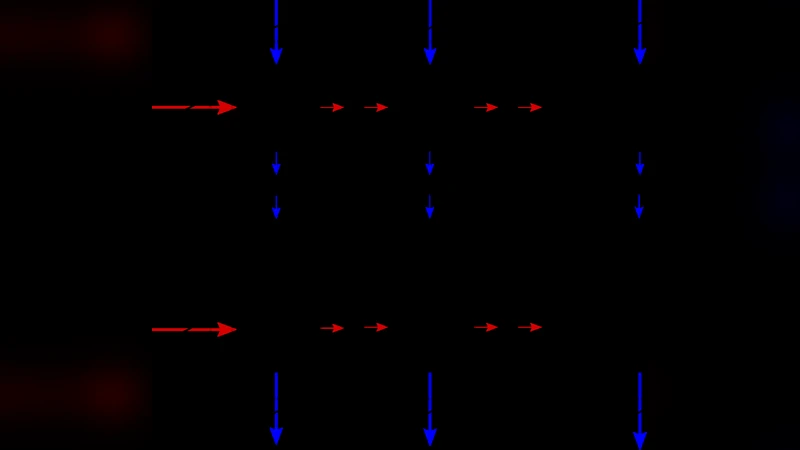

Gemmini 논문은 기존 DNN 가속기 연구가 하드웨어 설계에만 집중하고, SoC 레벨의 자원 경쟁, OS 오버헤드, 메모리 계층 구조 등 시스템 전반의 영향을 무시한다는 문제점을 명확히 제시한다. 이를 해결하기 위해 제안된 Gemmini는 세 가지 핵심 축을 갖는다. 첫째, 유연한 하드웨어 템플릿이다. 설계자는 systolic( TPU‑like) 혹은 vector(NVDLA‑like) 구조를 선택하고, PE 수, 타일 구조, 파이프라인 레지스터 삽입 여부 등을 파라미터화할 수 있다. 논문에서는 256 PE를 기준으로 두 가지 구현을 비교했는데, TPU‑like 설계는 주파수가 2.7배 높지만 면적·전력이 각각 1.8배·3배 더 크게 나타났다. 이러한 트레이드오프를 설계 단계에서 빠르게 탐색할 수 있다는 점이 큰 강점이다.

둘째, 다계층 소프트웨어 스택이다. 고수준에서는 ONNX 모델을 자동으로 파싱해 Gemmini 가속기에 매핑하는 툴체인을 제공하고, 저수준에서는 C/C++ API와 헤더 파일을 통해 PE 배열 크기, 스크래치패드 용량, 지원 데이터 플로우 등을 직접 제어한다. 특히 가상 메모리 지원을 내장해 TLB miss 비율을 실시간 프로파일링할 수 있다. 실험에서는 DNN 워크로드가 TLB miss를 20~30%까지 발생시키는 것을 확인했으며, 이를 기반으로 최소 TLB 엔트리만으로도 거의 최적에 가까운 성능을 달성하는 가상 주소 변환 설계를 제시한다.

셋째, 전체 SoC 통합이다. Gemmini는 Chipyard 프레임워크와 연동해 RISC‑V 인‑오더·아웃‑오더 CPU와 가속기를 하나의 칩에 배치한다. 다중 CPU·다중 가속기 구성, 버스 폭, L1/L2 캐시 크기·연관도 등 시스템 파라미터를 자유롭게 설정할 수 있다. 논문에서는 듀얼 코어 시스템에 각각 가속기를 연결하고, 메모리 파티셔닝을 조정해 DNN 레이어별 연산 특성에 맞는 캐시 할당 전략을 적용, 전체 성능을 8% 이상 향상시켰다. 또한 Linux OS 위에서 가속기를 사용하면서 발생한 비결정적 데드락과 페이지 테이블 교체 이슈를 발견해, 베어메탈 환경에서는 드러나지 않는 시스템‑레벨 버그를 조기에 식별할 수 있음을 강조한다.

전체적으로 Gemmini는 하드웨어·소프트웨어·시스템을 하나의 설계 흐름으로 묶어, 설계자와 연구자가 DNN 가속기의 실제 운영 환경을 정밀히 모델링하고 최적화할 수 있게 한다. 오픈소스 구현과 ASIC 실리콘(16 nm, 22 nm) 검증 결과는 제안된 전체 스택 접근법이 실용적이며, 기존 상용 가속기와 경쟁할 수 있는 성능을 제공함을 입증한다.

댓글 및 학술 토론

Loading comments...

의견 남기기