동적 뉴로모픽 프로세서로 구현한 시공간 특징 통합

초록

본 연구는 DYNAP‑SE 혼합‑신호 뉴로모픽 프로세서의 동적 시냅스를 이용해, 단일 포인트 뉴런이 여러 입력을 통합해 시공간 패턴을 선택적으로 검출할 수 있음을 보였다. 억제‑흥분 시냅스 쌍을 조합해 10 ms 수준의 EPSP 지연을 구현하고, 장치 불일치(device mismatch)를 활용해 다양한 지연값을 얻었다. 이를 통해 하나의 뉴런이 특정 ISI(Inter‑Spike Interval)를 가진 스파이크 시퀀스에만 강하게 반응하도록 설계하였다.

상세 분석

본 논문은 기존의 다중 구획(dendritic compartment) 모델이 요구하는 높은 회로 면적·전력 소모를 회피하면서, DYNAP‑SE 프로세서의 동적 시냅스(DPI 기반)를 활용해 시공간 특징 검출을 구현한다는 점에서 혁신적이다. 핵심 아이디어는 억제‑흥분 시냅스 쌍을 ‘디스인핽(Disynaptic) 지연 요소’로 활용하는 것으로, 억제 시냅스의 시간 상수(τ_inh)를 짧게, 흥분 시냅스의 시간 상수(τ_exc)를 길게 설정함으로써 억제 신호가 사라진 뒤에 남는 EPSP가 지연된 형태로 포스트시냅스 뉴런에 도달하도록 만든다.

이때 사용된 DPI 회로는 로그‑도메인 필터이며, 전류‑전압 변환을 통해 아날로그 전류를 생성한다. 논문은 표 I에 제시된 25개의 바이어스 파라미터를 조정해 τ_exc와 τ_inh를 정밀하게 제어했으며, 아날로그 회로 고유의 디바이스 매치 불일치가 오히려 다양한 지연값을 제공하는 ‘자연적 변이’를 만든다. 실험에서는 동일 뉴런 내의 서로 다른 CAM 주소에 연결된 시냅스 쌍이 각각 5 ~ 15 ms, 10 ~ 20 ms 등 서로 다른 지연을 보였으며, 이는 실제 생물학적 수상돌기 지연(10‑20 ms)과 일치한다.

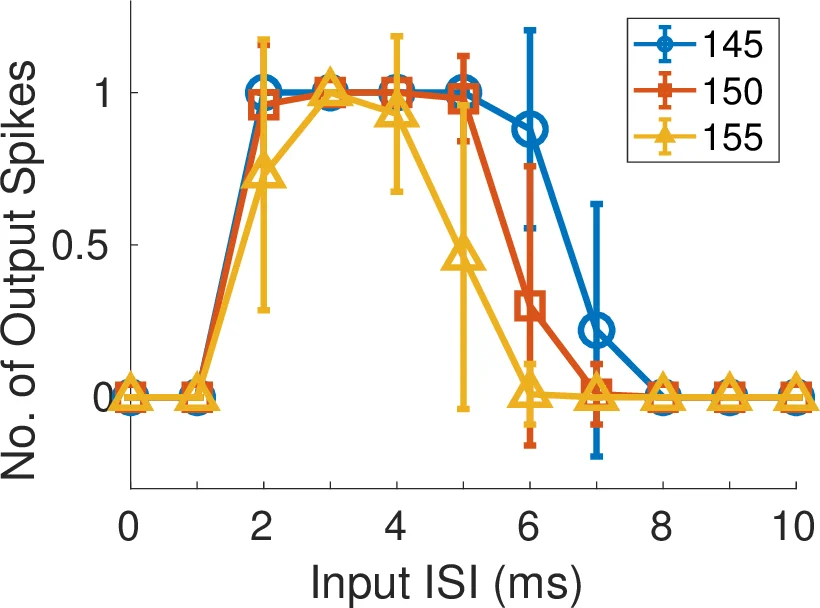

두 가지 패턴 검출 회로가 제안되었다. 첫 번째는 ‘페어‑셀렉티브’ 회로로, 두 개의 디스인핽 지연 요소에 각각 스파이크를 입력해 특정 ISI(예: 12 ms)에서 EPSP가 동시 최대치를 이루게 함으로써 뉴런이 중간 길이의 인터벌에만 반응하도록 설계했다. 두 번째는 ‘트리플렛‑셀렉티브’ 회로로, 세 개의 흥분 시냅스와 하나의 억제 시냅스를 이용해 연속된 스파이크 열(예: 5 ms 간격)과 억제 스파이크가 동시에 발생했을 때만 포스트시냅스 전압이 상승하도록 구현했다. 두 회로 모두 오프라인 Hebbian‑like 학습을 통해 최적의 시냅스 조합을 선택했으며, 실험 결과는 선택된 ISI 범위 내에서 뉴런 발화율이 현저히 증가하고, 범위를 벗어나면 거의 발화하지 않음을 보여준다.

이러한 접근법은 다음과 같은 장점을 가진다. ① 회로 규모가 작아 저전력·소형 디바이스에 적합하고, ② 아날로그 매치 불일치를 활용해 다중 지연을 자연스럽게 얻어 다채로운 시공간 필터링이 가능하며, ③ 포인트 뉴런 기반이므로 기존 SNN 프레임워크와 쉽게 통합될 수 있다. 반면, 지연값이 디바이스 변이에 크게 의존하므로 정확한 지연 제어가 어려우며, 복잡한 다중 구획 모델이 제공하는 비선형 공간 연산을 완전히 대체하기는 힘들다. 향후 연구에서는 디지털 보정 루프를 도입해 지연값을 정밀하게 튜닝하거나, 학습 메커니즘을 하드웨어에 내장해 실시간 적응형 시냅스 구성을 탐구할 필요가 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기