BERT 가속기 설계의 새로운 통찰

초록

본 논문은 BERT 학습 과정에서 나타나는 연산 특성을 정밀히 프로파일링하고, 매트릭스 연산 중심의 고성능 요구와 메모리 집약적 연산의 병존을 밝혀낸다. 또한 연산 이질성, 마이크로 배치·혼합 정밀도 기법의 확장성을 분석하여 차세대 가속기 설계에 필요한 하드웨어·소프트웨어 최적화 방안을 제시한다.

상세 분석

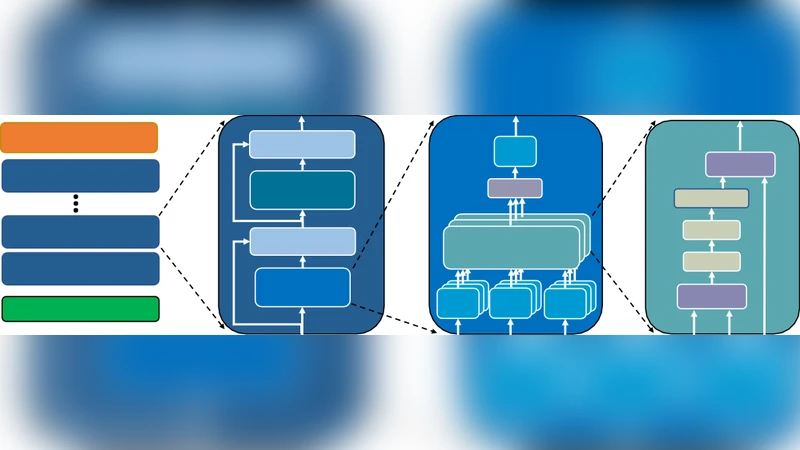

BERT 학습 워크로드를 상세히 조사한 결과, 기존 CNN 기반 모델과 마찬가지로 대규모 행렬 곱셈이 전체 실행 시간의 60 % 이상을 차지한다는 점이 확인되었다. 그러나 BERT는 Transformer 블록 내부에서 Self‑Attention 메커니즘과 Feed‑Forward Network(FFN)를 반복적으로 수행하면서, 특히 Q·K·V 행렬 생성·정규화 단계와 Softmax 연산, 그리고 레이어 정규화(LayerNorm)와 같은 메모리‑집중 연산이 전체 메모리 대역폭 사용량의 30 % 이상을 차지한다는 새로운 사실을 발견했다. 이러한 연산은 연산량이 상대적으로 적지만, 데이터 접근 패턴이 비연속적이며, 캐시 재사용률이 낮아 메모리 지연(latency)과 대역폭 병목을 초래한다.

또한, BERT의 각 Transformer 레이어는 연산 강도가 크게 다르다. 예를 들어, 초기 레이어에서는 Self‑Attention 연산이 주를 이루지만, 깊은 레이어에서는 FFN의 2‑step MLP 연산이 비중을 높인다. 이 이질성은 동일한 하드웨어 자원을 일관되게 활용하기 어렵게 만들며, 동적 전력 관리와 연산 스케줄링 최적화가 필요함을 시사한다.

마이크로 배치(Micro‑batching)와 혼합 정밀도(Mixed‑Precision) 학습 기법을 적용하면, 연산 밀도를 높이고 메모리 요구량을 감소시킬 수 있다. 특히, FP16·BF16 변환을 통해 행렬 연산의 데이터 전송량을 절반 이하로 줄이면서도 모델 정확도 손실을 최소화한다. 그러나 정밀도 변환 과정에서 발생하는 스케일링 오버플로와 언더플로를 방지하기 위해 동적 스케일링 로직과 손실 스케일링(Loss Scaling) 메커니즘이 필수적이다.

분산 학습 환경을 고려하면, 파라미터 서버 방식보다 All‑Reduce 기반의 데이터 병렬 방식이 통신 효율이 높다. 하지만 BERT와 같은 대형 모델에서는 통신량이 급증하므로, 통신‑연산 겹침(overlap)과 압축(Gradient Compression) 기술이 가속기 설계에 중요한 요소가 된다.

종합적으로, BERT 가속기 설계는 다음 네 가지 핵심 요구사항을 만족해야 한다. 첫째, 대규모 행렬 연산을 위한 고대역폭 메모리 서브시스템과 효율적인 GEMM 엔진; 둘째, 메모리‑집중 연산을 위한 저지연 캐시 구조와 레이어 정규화 전용 유닛; 셋째, 연산 이질성을 감지하고 동적으로 리소스를 재배치할 수 있는 스케줄러; 넷째, 혼합 정밀도와 마이크로 배치를 원활히 지원하는 데이터 경로와 스케일링 로직이다. 이러한 설계 지침은 향후 더욱 깊고 넓은 Transformer 기반 모델이 등장함에 따라 확장 가능성을 확보한다.