저전압 디바이스가 병렬 시스템 에너지 효율에 미치는 이점

초록

본 논문은 저전압 동작 모드를 지원하는 프로그래머블 회로에서 에너지 효율을 극대화하려면 소프트웨어, 특히 병렬 프로그램의 품질이 핵심임을 강조한다. 저전압·저주파 운영과 코어 수 확대를 결합한 모델을 제시하고, 수학적 분석과 Sniper·McPAT 시뮬레이션을 통해 병렬 코드가 잘 작성될수록 전력 소비와 공급 전압을 크게 낮출 수 있음을 입증한다.

상세 분석

논문은 먼저 현대 프로세서가 전통적인 클럭·전압 스케일링 한계에 도달했으며, 에너지 효율 향상을 위해 저전압(near‑threshold) 동작이 필요함을 지적한다. 이때 소프트웨어 레이어가 하드웨어 자원 사용에 미치는 영향을 무시할 수 없으며, 특히 병렬화 수준이 높은 애플리케이션은 코어 수를 늘려 성능을 유지하면서 전압과 주파수를 낮출 여지를 제공한다. 저전압 동작은 전력 P가 전압 V의 제곱(또는 거의 세제곱) 비례한다는 CMOS 전력 공식 P = k₁·a·C·V²·F + I_leak·V에 기반한다. 따라서 전압을 약 30 % 낮추면 전력은 50 % 이상 감소한다.

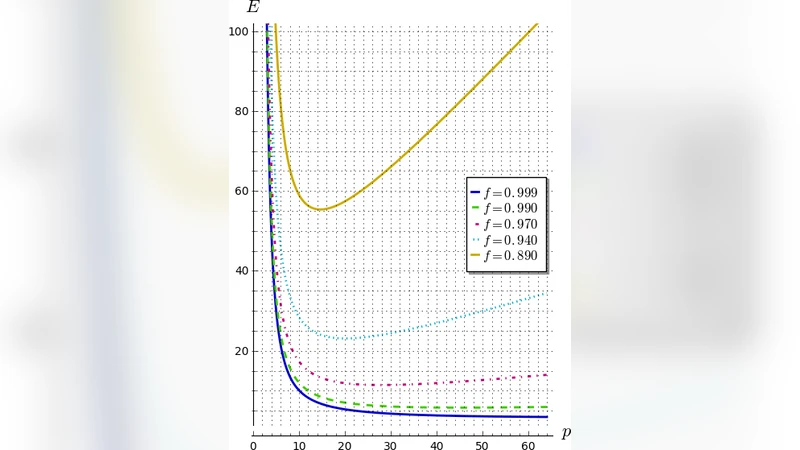

논문은 이를 정량화하기 위해 다음 네 단계 방법론을 제시한다. (i) 전력·주파수 관계식 F_max = k₂·(V−V_th)^h / V (h≈1.5)를 이용해 목표 성능에 맞는 최소 전압 V_p를 계산하고, (ii) 병렬 코어 수 p와 목표 속도 향상 비율 S_p를 이용해 필요한 주파수 F_p = S_p·F_s / T_r을 도출한다. 여기서 T_r은 목표 실행 시간 비율이며, 예를 들어 T_r=0.5는 두 배 빠른 실행을 의미한다. (iii) 위 식들을 결합해 전체 에너지 E = p·P·T_p 를 구한다. 이때 사용되지 않은 코어는 전력 차단(gating)으로 무시한다.

수치 분석에서는 64코어(16타일·4코어) 구조와 Black‑Scholes 벤치마크를 사용했으며, 파라미터 k₁·a·C=1.06×10⁻⁸, I_leak=7.97×10⁻² A, V_th=0.23 V, k₂=4.02×10⁻⁹, F_s=3.2 GHz, V_s=1.2 V 등을 적용했다. 결과는 두 가지 주요 현상을 보여준다. 첫째, 코어 수를 늘릴수록 에너지 소비가 급격히 감소하고, 동시에 공급 전압도 크게 낮아진다. 둘째, 애플리케이션의 병렬 비율 f가 클수록 최적 전압과 에너지 절감 폭이 커진다. 즉, 병렬화가 잘된 코드가 저전압 동작의 이점을 최대한 활용한다. 반면, 병렬성이 낮은 코드(f가 작음)는 최적점이 높은 전압·낮은 코어 수에서 나타나며, 저전압의 이점이 제한적이다.

시뮬레이션 결과는 Sniper와 McPAT을 통해 분석 모델을 검증했으며, Black‑Scholes를 T_r=1(단일 코어와 동일 성능)에서 실행했을 때 측정된 에너지가 모델 곡선과 일치함을 확인했다. 이는 제시된 수학적 프레임워크가 실제 시스템 설계와 에너지 추정에 신뢰성을 제공함을 의미한다.

결론적으로, 저전압 디바이스와 다중 코어 아키텍처를 결합한 에너지 절감 전략은 소프트웨어 수준, 특히 병렬 코드의 품질에 크게 의존한다. 개발자는 병렬화와 저전압 동작을 동시에 고려한 설계·코딩 가이드라인을 마련해야 하며, 이를 통해 전력 제한이 심한 IoT·엣지 컴퓨팅 환경에서도 성능을 유지하면서 에너지를 크게 절감할 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기