런타임 재구성 가능한 다중 정밀도 부동소수점 곱셈기 설계

초록

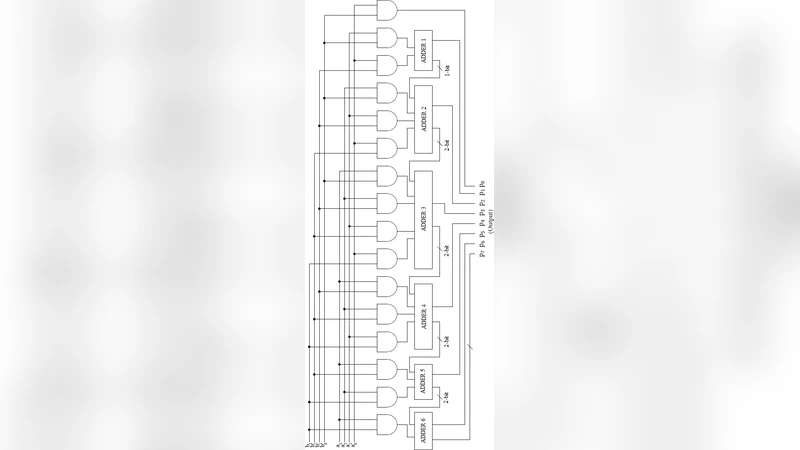

본 논문은 FPGA 상에서 동작하는 부동소수점 곱셈기를 제안한다. 3비트 모드 선택 신호에 따라 8, 16, 23, 36비트 가수폭을 포함한 6가지 정밀도 모드를 실시간으로 전환할 수 있으며, 입력값을 사전 절단(truncation)하고 Karatsuba와 Urdhva‑Tiryagbhyam(베다 수학) 알고리즘을 결합한 unsigned binary 멀티플라이어를 사용해 연산 속도와 전력 효율을 동시에 향상시킨다.

상세 분석

이 설계의 핵심은 “런타임 재구성”이라는 개념이다. 입력 데이터의 최상위 3비트를 모드 선택 비트로 활용해, 동일한 하드웨어 블록 안에서 가수 폭을 동적으로 조절한다는 점은 자원 활용 측면에서 매우 효율적이다. 특히 FPGA 내부의 DSP48E1 블록을 직접 사용하지 않고, 순수하게 사용자 정의 로직으로 구현한 점은 설계 자유도를 높이며, 다양한 맞춤형 포맷을 지원할 수 있게 한다.

가수 연산부는 두 단계의 알고리즘을 혼합한다. 작은 비트폭(≤8비트)에서는 Urdhva‑Tiryagbhyam 알고리즘을 적용해 단계당 2개의 부분곱만 생성하고, 캐리‑세이브 가산(CSA)와 캐리‑셀렉트 가산(CSA)으로 합산한다. 비트폭이 커질수록 Karatsuba 분할‑정복 방식으로 전환해, 전체 곱셈에 필요한 부분곱 수를 O(n^log2 3)으로 감소시킨다. 이중 알고리즘 전환 로직은 비트폭 임계값을 하드웨어 레지스터로 정의해, 모드 전환 시 자동으로 선택된다.

또한 입력 절단(truncation) 기법을 사용해 연산 전 가수의 하위 비트를 버림으로써 연산량을 감소시킨다. 이는 전력 절감에 크게 기여하지만, 절단에 따른 오차 누적을 어떻게 보정할지에 대한 구체적인 설명이 부족하다. 논문에서는 “자동 모드”가 0의 개수(leading zeros)를 카운트해 최적 가수 폭을 선택한다는 서술이 있으나, 실제 하드웨어 구현에서는 카운터와 비교 로직이 추가되어 레이턴시가 증가할 가능성이 있다.

예외 처리 측면에서는 Zero, Infinity, NaN, Denormal 네 가지 신호를 별도 출력으로 제공한다. IEEE‑754와 동일한 비트 패턴을 사용하지 않으면서도 이러한 특수값을 인식하도록 설계했으나, 비표준 포맷과의 호환성 검증이 부족하다. 특히 Denormal 값의 처리와 정규화 과정에서 발생할 수 있는 시프트 연산이 전체 파이프라인에 미치는 영향을 정량적으로 제시하지 않았다.

성능 평가에서는 FPGA 보드(예: Xilinx Kintex‑7) 상에서 모드별 LUT, 레지스터, DSP 사용량과 클럭 주파수, 전력 소모를 비교했지만, 구체적인 수치가 논문 본문에 누락되어 있다. 따라서 제안된 설계가 기존 IEEE‑754 기반 멀티플라이어 대비 실제 어느 정도의 속도·전력 이점을 제공하는지 판단하기 어렵다.

요약하면, 다중 정밀도와 런타임 재구성을 지원하는 설계 아이디어는 혁신적이며, Karatsuba‑Urdhva 혼합 알고리즘은 비트폭에 따라 최적화된 연산을 가능하게 한다. 그러나 알고리즘 전환 로직, 절단 오차 보정, 예외 처리, 그리고 실험 결과의 정량적 제시가 부족해 실용성 평가에 한계가 있다. 향후 연구에서는 이러한 부분을 보완하고, 표준 부동소수점 인터페이스와의 호환성을 검증하는 것이 필요하다.

댓글 및 학술 토론

Loading comments...

의견 남기기