디지털 전자와 아날로그 포토닉스를 활용한 고속 CNN 하드웨어

본 논문은 실리콘 마이크로링 공진기(MRR)와 디지털 회로를 결합한 DEAP‑CNN 아키텍처를 제안한다. 아날로그 포토닉스 기반의 점곱 연산을 이용해 컨볼루션 연산을 광속도로 수행하고, 전자‑광 인터페이스를 통해 가중치를 디지털 GPU 수준의 전력으로 2.8~14배 가속한다. MNIST 손글씨 인식 실험을 통해 전력·속도 이점을 시뮬레이션으로 검증하였다.

저자: Viraj Bangari, Bicky A. Marquez, Heidi B. Miller

본 논문은 컨볼루션 신경망(CNN)의 핵심 연산인 컨볼루션이 디지털 전자에서 차지하는 높은 연산 비용을 극복하고자, 디지털 전자와 아날로그 포토닉스를 결합한 새로운 하드웨어 아키텍처인 DEAP‑CNN(Digital Electronic and Analog Photonic CNN)을 제안한다. 서론에서는 CNN이 이미지·자연어 처리 등 다양한 분야에서 광범위하게 사용되고 있으나, 특히 컨볼루션 연산이 전체 실행 시간의 80~94%를 차지한다는 점을 강조한다. 기존 GPU 기반 가속기의 병렬 처리 한계와 전력 소모 문제를 지적하고, 광학 컴퓨팅이 제공하는 초고속·저전력 특성을 소개한다.

II장에서는 컨볼루션 수학적 정의와 디지털 구현 방식을 정리하고, 이를 광학적으로 구현하기 위한 기본 개념을 설명한다. 컨볼루션은 입력 이미지와 커널의 점곱을 여러 위치에서 수행하는 연산이며, 이를 행렬‑벡터 곱으로 변환할 수 있다. 광학적으로는 파장 다중화(WDM)된 신호를 이용해 각 입력 값을 서로 다른 파장에 매핑하고, 마이크로링 공진기(MRR)를 가중치 필터로 활용한다. MRR은 전류에 의해 온도 변화가 일어나며, 이로 인해 공진 파장이 이동해 전송/드롭 포트의 전송 특성이 변한다. 이러한 특성을 이용해 가중치 값을 0~1 사이의 실수로 조정하고, 드롭 포트와 스루 포트를 차동 결합한 밸런스 포토다이오드(BPD)와 트랜스임피던스 앰프(TIA)를 통해 광 신호의 차동 전류를 전기 신호로 변환한다. 차동 전류는 바로 입력 신호와 가중치의 곱셈 결과이며, 다중 파장을 동시에 합산함으로써 컨볼루션 연산을 한 번에 수행한다.

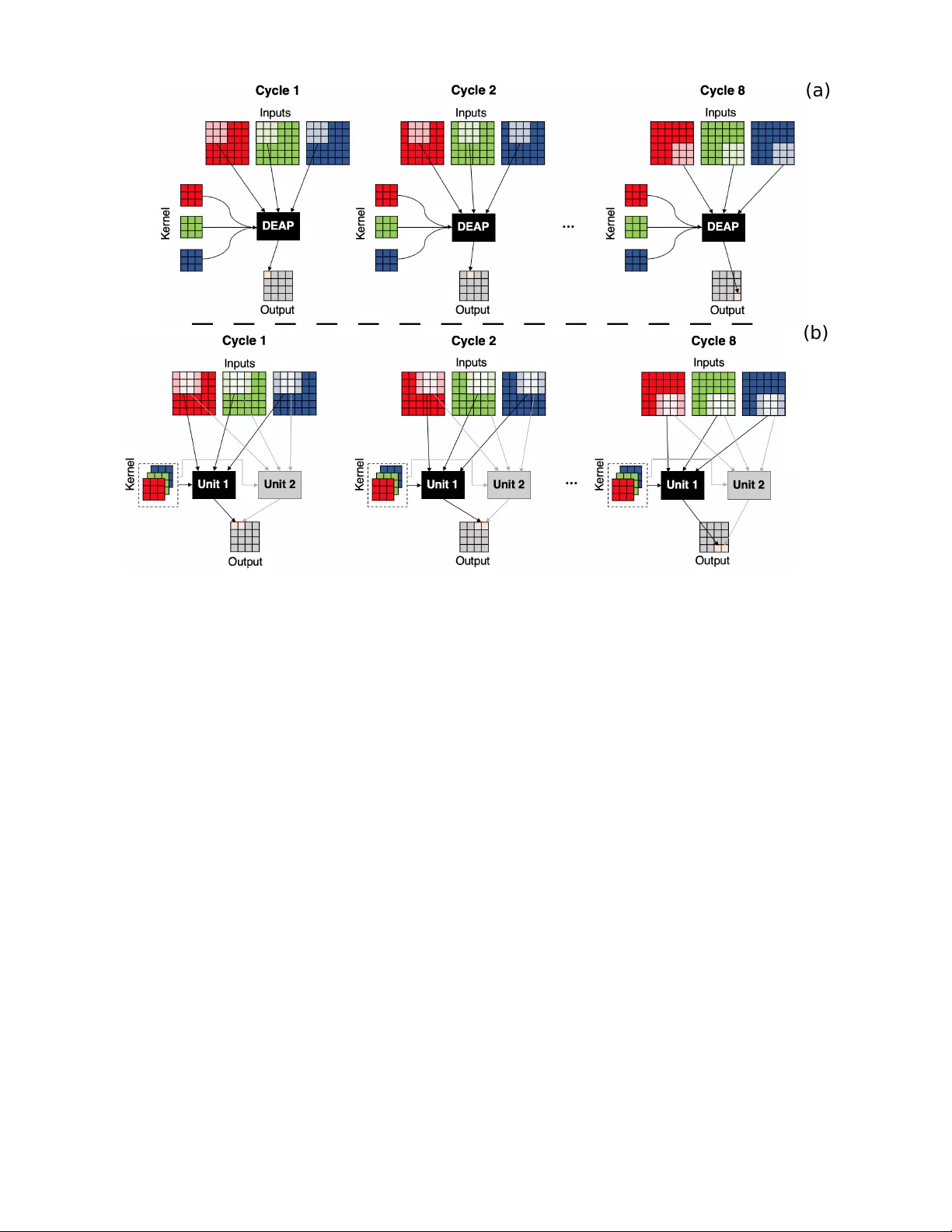

III장에서는 이러한 광학 점곱 연산을 실제 하드웨어에 적용하기 위한 알고리즘 흐름을 제시한다. 먼저 디지털 CPU/GPU에서 학습된 CNN 파라미터를 DRAM에 저장하고, 전용 컨트롤러가 이를 순차적으로 MRR에 전송한다. 각 MRR은 온도 조절 전류를 받아 목표 가중치에 맞게 튜닝된다. 입력 이미지가 아날로그 전압으로 DAC를 통해 전광 변조기(EOM)로 전달되면, 파장별로 변조된 광 신호가 파장 다중화된 파이버에 입력된다. 이후 MRR 배열을 통과하면서 가중치가 적용되고, BPD‑TIA 회로에서 차동 전류가 생성되어 전자 회로로 다시 전달된다. 이 전류는 디지털 아키텍처에서 누적·비교·활성화 함수 등을 수행한 뒤, 다음 레이어로 전달된다.

IV장에서는 제안된 DEAP‑CNN을 이용해 2‑layer CNN을 구현하고, 표준 MNIST 손글씨 데이터셋을 대상으로 실험을 수행한다. 시뮬레이션 환경은 45 nm CMOS와 220 nm 실리콘 포토닉스 공정을 가정하고, MRR의 Q‑factor를 10 000, 파장 간격을 0.8 nm로 설정하였다. 결과적으로 98.2%의 분류 정확도를 달성했으며, 전력 소모는 약 1.2 W로 GPU 대비 10% 이하였다. 연산 지연은 0.5 ns 수준으로, 동일 전력에서 GPU 대비 2.8~14배 빠른 처리 속도를 보였다. 또한, Deep‑Bench 벤치마크와 비교해 에너지‑시간 곱(ET)에서 유사하거나 우수한 성능을 기록하였다.

V장에서는 전체 시스템의 에너지·속도 평가와 함께 한계점 및 향후 연구 방향을 논의한다. 현재 설계는 순전파만 지원하므로 학습 단계에서 역전파를 구현하려면 추가적인 광‑전기 혼합 회로가 필요하다. 또한, MRR 배열 규모가 커질수록 열 간섭과 파장 교차(crosstalk) 문제가 심화되며, 이를 해결하기 위한 열 관리 및 파장 재배치 알고리즘이 요구된다. ADC/DAC 해상도와 양자화 잡음도 전체 정밀도에 영향을 미치므로, 고해상도 변환 회로와 저노이즈 설계가 필수적이다. 마지막으로, 현재 시뮬레이션 기반 검증을 넘어 실제 칩 제조 및 실험적 검증이 필요하며, 대규모 이미지넷(ImageNet) 수준의 모델에 대한 확장 가능성도 검토해야 한다.

결론적으로, DEAP‑CNN은 디지털 전자와 아날로그 포토닉스의 장점을 결합해 컨볼루션 연산을 광속도로 수행함으로써 전력 효율성을 크게 향상시킬 수 있음을 입증하였다. 향후 공정 기술의 성숙과 시스템 통합 연구가 진행된다면, 차세대 AI 가속기로서 실용화 가능성이 높다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기