임베디드 RISC V 코어의 초고속 모듈러 곱셈

초록

본 논문은 IoT 디바이스에 적합하도록 RISC‑V 기반 마이크로프로세서에 Montgomery 곱셈 전용 커스텀 명령(MMUL)을 추가하고, 명령을 원자적으로 실행하거나 반복적인 짧은 단계로 나누는 부분 실행 모드를 제공한다. ASIC에서는 136 MHz, FPGA에서는 81 MHz에서 128‑bit 연산을 수행하며, 기존 소프트웨어 대비 최대 13배 가속, 동적 전력은 최대 95% 절감한다. 면적은 기본 코어 대비 41 %(FPGA)·49 %(ASIC) 증가한다.

상세 분석

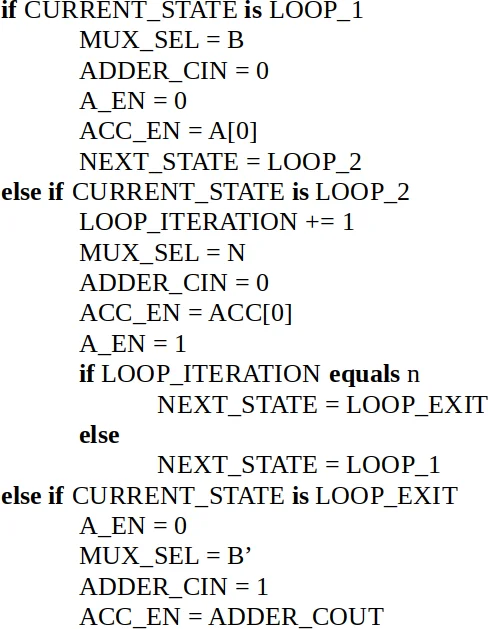

이 연구는 경량 IoT 노드가 요구하는 저전력·저면적을 유지하면서 공개키 암호에 필수적인 대규모 정수 연산을 가속하는 방법을 제시한다. 핵심 아이디어는 RISC‑V RV32EC ISA에 ‘MMUL’이라는 새로운 커스텀 명령을 삽입하는 것이다. MMUL은 메모리 주소 3개(피연수2·피연수·모듈러스)와 피연산자 비트 길이를 인코딩한 필드로 구성되며, R‑type, I‑type, R4‑type 등 기존 포맷을 활용해 설계자가 메모리 레이아웃에 구애받지 않도록 R4‑type을 선택하였다. 하드웨어 구현은 Radix‑2 Montgomery Multiplication(R2MM) 알고리즘을 기반으로 하며, 각 반복(iteration)마다 2클록 사이클을 사용한다. 전체 연산은 2·n + 1 사이클(여기서 n은 피연산자 비트 수)와 메모리 접근 비용으로 구성된다.

명령을 원자적으로 실행하면 CPU는 MMUL이 끝날 때까지 인터럽트를 처리하지 못해 실시간 응답성이 저하될 수 있다. 이를 해결하기 위해 ‘부분 실행(Partial Execution)’ 모드를 도입했는데, 이는 CSR(Control‑Status‑Register)3에 플래그를 설정해 MMUL이 한 비트씩 처리하고 즉시 명령을 retire하도록 만든다. 소프트웨어는 n번의 MMUL 호출을 수행하고, 각 호출 사이에 인터럽트가 발생할 수 있다. 부분 실행 시 최대 지연은 메모리 로드/스토어 3·W cycles + 2 cycles 정도로 크게 감소한다. 루프 언롤링과 결합하면 원자 실행과 거의 동일한 성능을 유지하면서 실시간성을 확보한다.

성능 평가에서는 FourQ(128‑bit), NIST P‑256, Curve25519(256‑bit) 등 대표적인 ECC 곡선을 대상으로 소프트웨어 구현과 비교했다. 전체 소프트웨어 대비 9 ~ 13배 가속을 달성했으며, 동적 전력은 0.064 W(CI‑AE)·0.120 W(CI‑PE) 등 최대 95 % 절감 효과를 보였다. 면적 측면에서는 FPGA에서 슬라이스 487→649(33 % 증가), ASIC에서는 플립플롭·게이트 872/8106→1305/12105(49 % 증가)였으며, 클럭 주파수는 각각 9 %·8 % 감소했다. 이러한 오버헤드는 기존 경량 블록 암호 가속기(≈58 % 면적 증가)와 비교해도 경쟁력이 있다.

결론적으로, 커스텀 명령을 통한 모듈러 곱셈 가속은 하드웨어 복잡도를 크게 늘리지 않으면서도 실시간 응답성을 유지할 수 있는 실용적인 설계 방안임을 입증한다.

댓글 및 학술 토론

Loading comments...

의견 남기기