디랙 위상 물질을 위한 행렬 프리 스텐실 DSL 및 고성능 코드

초록

PVSC‑DTM은 디랙 및 위상 절연체와 같은 물질을 행렬을 저장하지 않고 스텐실 형태로 계산하도록 설계된 도메인‑특화 언어와 코드 생성기이다. MPI와 OpenMP를 결합한 하이브리드 병렬 구조와 SIMD 벡터화를 통해 기존 행렬 기반 구현보다 노드 수준에서 현저히 빠른 성능을 보이며, 루프 밸런스와 메모리 대역폭 활용 측면에서 루프라인 모델에 근접한다. 그래핀 양자점 배열에서의 파동 산란, 강한 위상 절연체의 내부 고유값 계산, 무질서한 웨일 반금속의 광전자 스펙트럼 등 세 가지 물리 응용 사례를 통해 프레임워크의 유용성을 입증한다.

상세 분석

PVSC‑DTM은 물리학적 스텐실 연산을 직접 코드로 변환하는 DSL을 제공함으로써, 전통적인 CSR 혹은 COO 형태의 희소 행렬을 메모리에 저장하고 접근하는 방식을 완전히 배제한다. 이는 메모리 대역폭이 제한적인 현대 멀티코어 CPU에서 연산량 대비 메모리 트래픽을 최소화하는 핵심 전략이다. DSL은 격자 차원, 스핀·오비탈 자유도, 근접 이웃 범위 등을 선언적으로 기술하게 하여, 코드 생성 단계에서 자동으로 최적 블록 크기와 데이터 레이아웃을 결정한다. 자동 블록킹은 머신 레벨의 L1/L2 캐시 용량과 메모리 대역폭 모델을 입력으로 하여, 루프당 플롭/바이트 비율을 루프라인 모델의 이론적 한계에 가깝게 만든다.

생성된 코드는 MPI 기반 도메인 분할과 OpenMP 스레드 레벨의 공유 메모리 병렬화를 동시에 적용한다. 각 MPI 프로세스는 3차원 격자 블록을 담당하고, 내부 루프는 SIMD 명령어(AVX2/AVX‑512)를 활용해 4~8배의 벡터 폭을 확보한다. 특히, 스텐실 연산은 인접 셀에 대한 고정된 패턴을 가지므로, 컴파일러가 루프 전개와 메모리 프리패칭을 효율적으로 수행하도록 어셈블리 수준에서 인스트럭션 스케줄링을 제어한다.

성능 평가에서는 두 종류의 인텔 Xeon(IVB, BDW) 노드에서 spMVM(희소 행렬‑벡터 곱)과 다중 벡터 연산을 벤치마크하였다. 결과는 메모리 대역폭의 85~95%를 활용했으며, 동일 연산을 행렬 기반 GHOST 라이브러리와 비교했을 때 2.5배 이상 빠른 실행 시간을 기록했다. 또한, 500노드 규모의 클러스터에서 강한 스케일링 테스트를 수행했을 때 90% 이상의 효율을 유지, 통신 오버헤드가 최소화된 점이 강조된다.

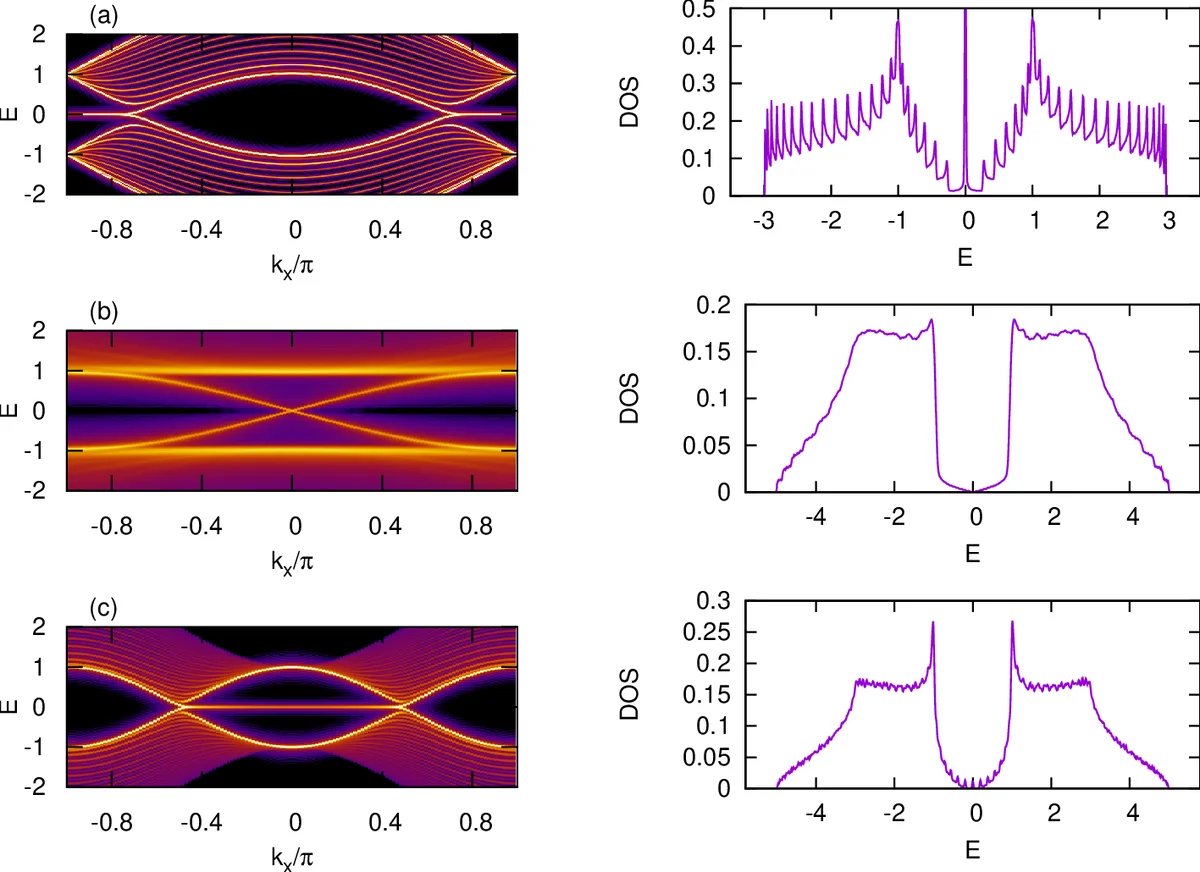

물리 응용 측면에서는 (i) 그래핀 양자점 배열에서 디랙 파동의 산란을 시뮬레이션하여 전자 전도도와 전자 파동 간섭 패턴을 정량화했으며, (ii) 3차원 강한 위상 절연체 모델에 대해 수천 개의 내부 고유값을 커널 폴리노미얼 방법(KPM)과 결합해 효율적으로 추출, 표면 상태와 벌크 밴드 간의 토폴로지 전이 현상을 상세히 분석했다. (iii) 무질서한 웨일 반금속에서는 무작위 전위와 결합된 스텐실 연산을 통해 광전자 스펙트럼을 계산, 페르미 아크와 벌크 웨일 노드의 상호작용을 시각화하였다. 이러한 사례는 PVSC‑DTM이 복잡한 토폴로지 물질의 전자 구조 계산에 있어 메모리 효율성과 확장성을 동시에 제공함을 입증한다.

전반적으로, DSL 기반 자동 코드 생성, 행렬‑프리 스텐실 구현, 그리고 하이브리드 SIMD‑MPI‑OpenMP 병렬화 전략이 결합된 PVSC‑DTM은 현대 HPC 환경에서 토폴로지 물질 시뮬레이션을 수행하는 연구자들에게 강력하고 사용하기 쉬운 도구로 자리매김한다.

댓글 및 학술 토론

Loading comments...

의견 남기기