M3D 통합으로 DRAM 지연과 면적 트레이드오프 극복

초록

본 논문은 기존 2D DDR4 DRAM에서 발생하는 지연‑면적 트레이드오프를 완화하기 위해, 거친 입자 단위의 단일칩 3차원(M3D) 적층 기술을 활용한 새로운 셀 배열 구조를 제안한다. 설계된 M3D DRAM은 접근 경로의 임계 길이를 단축함으로써 평균 지연을 최대 9.56 % 감소시키고, 전력 소비를 4.96 % 절감하며, 에너지‑지연 곱(EDP)을 21.21 % 낮춘다. 또한 동일 용량 대비 다이 면적을 최대 14 % 줄일 수 있음을 PARSEC 벤치마크 기반 실험을 통해 입증한다.

상세 분석

DRAM 설계에서 지연과 면적은 서로 상쇄되는 관계에 놓여 있다. 기존 2D 구조는 밀도를 높이기 위해 셀 배열을 평면에 촘촘히 배치하지만, 이때 비트라인·워드라인 길이가 길어져 전하 이동에 소요되는 RC 지연이 증가한다. 논문은 이러한 “임계 길이(critical length)”를 감소시키는 것이 지연 개선의 핵심임을 강조하고, 이를 위해 M3D(단일칩 3D) 적층 기술을 도입한다. M3D는 동일 실리콘 웨이퍼 내에서 여러 층을 수직으로 적층하되, 층간 연결을 미세 금속 TSV 대신 고밀도 마이크로볼트(μ‑bump) 방식으로 구현한다. 이 방식은 층간 피치가 수십 나노미터 수준으로 얇아져, 셀 배열을 수직으로 재배치하면서도 면적 효율을 유지한다.

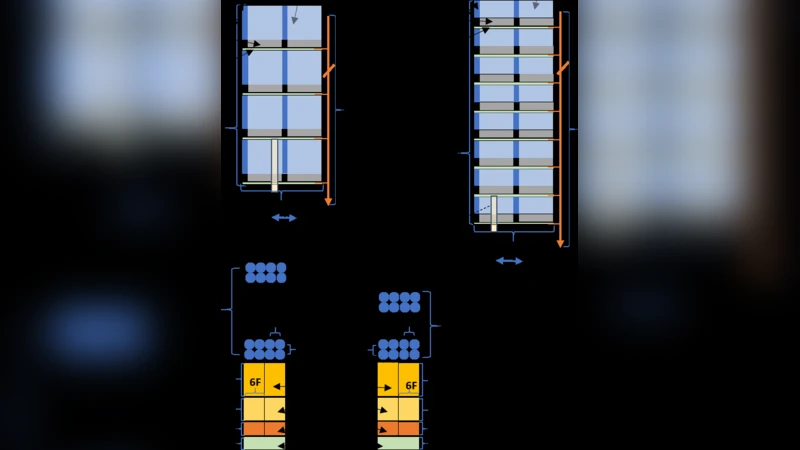

구체적으로 저자들은 두 가지 M3D 기반 셀 배열 조직을 설계한다. 첫 번째는 “수직 비트라인” 구조로, 기존 평면 비트라인을 대신해 층간 비트라인을 형성해 비트라인 길이를 30 % 이상 단축한다. 두 번째는 “수직 워드라인” 구조로, 워드라인을 수직으로 스택함으로써 워드라인 길이와 셀 선택 지연을 동시에 감소시킨다. 두 구조 모두 전통적인 2D DDR4와 동일한 용량·대역폭을 제공하면서도, 전기적 RC 모델링과 회로 시뮬레이션을 통해 지연 감소 효과를 정량화한다.

평가 단계에서는 PARSEC 벤치마크 집합을 메모리 서브시스템 시뮬레이터에 입력해, 실제 워크로드에서의 평균 메모리 접근 지연, 전력 소비, 에너지‑지연 곱(EDP)을 측정한다. 결과는 M3D DRAM이 평균 지연을 9.56 % 감소시키고, 전력은 4.96 % 절감하며, EDP는 21.21 % 개선함을 보여준다. 특히 면적 측면에서는 다이 면적을 14 %까지 축소할 수 있어, 고밀도 서버·모바일 시스템에서 비용·전력 효율성을 동시에 향상시킬 수 있다.

하지만 논문은 M3D 적층 공정의 제조 비용, 열 관리, 그리고 TSV 대체 연결의 신뢰성 문제를 완전히 해결하지는 못한다. 또한, 수직 구조가 기존 메모리 컨트롤러와 호환성을 유지하기 위해 추가적인 인터페이스 변환 로직이 필요할 수 있다. 이러한 한계에도 불구하고, 제안된 설계는 DRAM 기술 로드맵에서 “지연‑면적” 딜레마를 완화하는 실용적인 경로를 제시한다는 점에서 큰 의미를 가진다.