TPU 제조 결함의 확률적 영향 분석 및 모델링

초록

본 논문은 구글 TPU의 systolic array 기반 매트릭스 곱셈 유닛에 발생할 수 있는 영구 결함을 이산시간 마코프 체인(DTMC)으로 형식화하고, PRISM 모델 체커를 이용해 결함이 DNN 추론 정확도에 미치는 확률적 영향을 정량적으로 평가한다. 결함 종류(스턱‑앳‑0/1), 비트 위치, 결함이 발생한 MAC 유닛의 행·열 위치, 그리고 네트워크 레이어 수가 오류 확률에 미치는 상관관계를 실험적으로 검증한다.

상세 분석

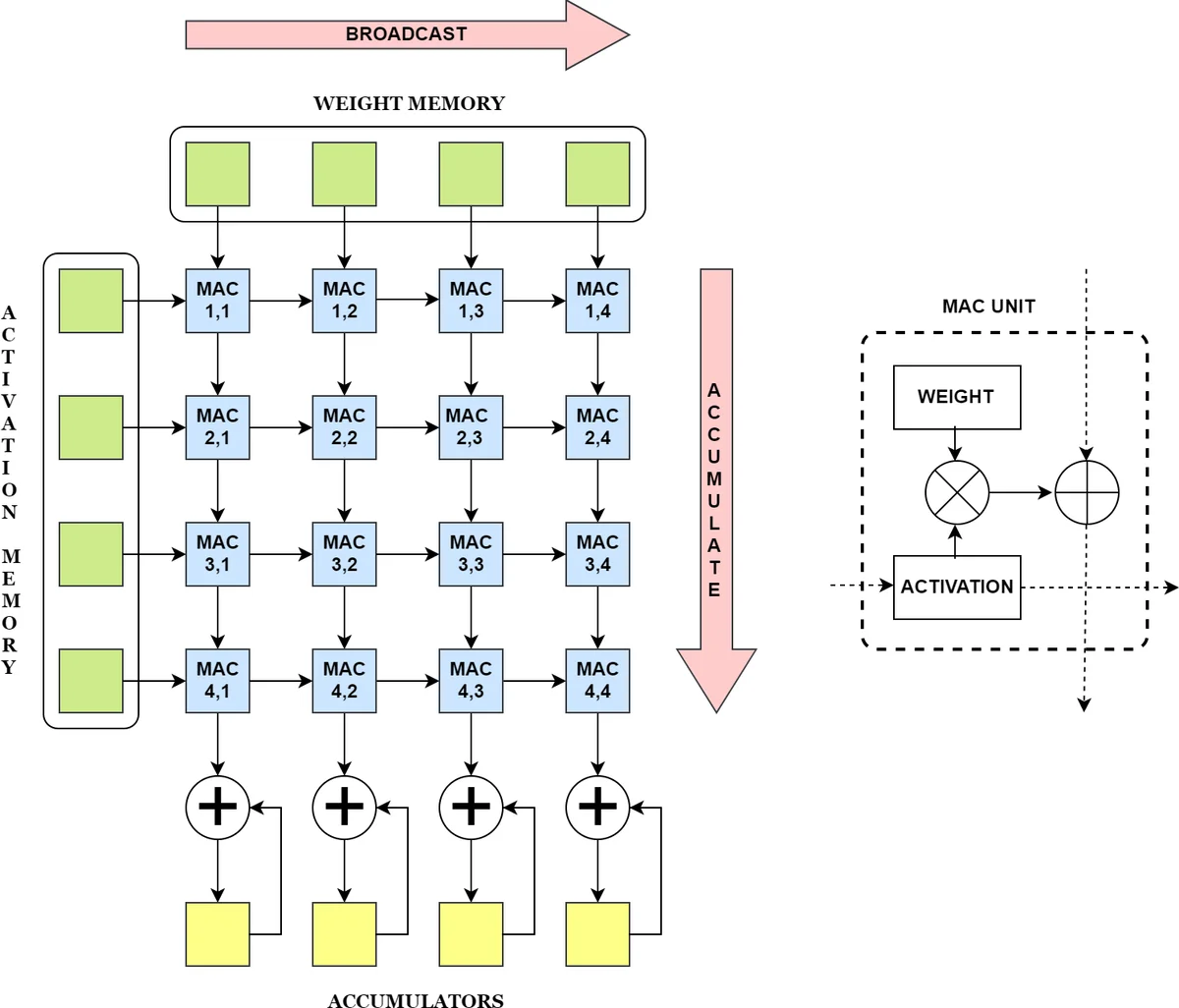

이 논문은 TPU와 같은 고성능 DNN 가속기의 제조 결함을 정량적으로 분석하기 위해 세 가지 핵심 기법을 결합한다. 첫째, 영구 결함을 “스턱‑앳‑0/1” 형태의 비트 오류로 모델링하고, 이를 MAC 유닛의 가중치 레지스터, 곱셈기, 누산기 각각에 적용한다. 결함이 발생한 MAC 유닛을 F MAC₍r,c₎라 정의하고, 효과적인 연산 영역(effective area) 내에 위치할 경우에만 오류가 전파된다는 가정을 통해 수학적 오류 전파식을 (5)(7)로 도출한다. 여기서 C₀C₇과 같은 논리 조건은 결함이 마스크되는 경우와 누설(leak) 효과가 발생하는 경우를 구분한다. 특히, 누산기·곱셈기에서 스턱‑앳‑1이 발생하면, 해당 MAC 유닛이 비활성 단계에서도 고정값 Sₘ을 출력해 아래쪽 MAC 유닛으로 전달되는 “leak” 현상을 모델링함으로써 실제 하드웨어에서 관찰되는 오버플로우와 비선형 왜곡을 정밀히 포착한다.

둘째, 입력 선택 과정을 확률적 자동자(IS‑DTMC)로 표현한다. 입력 비트 b에 따라 2ᵇ개의 상태를 갖는 마코프 체인을 구성하고, 각 상태 전이 확률 pₖ를 통해 입력 분포를 정의한다. 이는 N개의 입력 뉴런에 대해 병렬 합성(parallel composition)되어 전체 입력 벡터 X(1)의 확률 공간을 정확히 기술한다.

셋째, 전체 연산 흐름을 TPU‑FA( fault‑analysis) 자동자로 모델링한다. 이 자동자는 초기화, systolic array 연산, 활성화·양자화, 오류 검증 네 단계로 구성되며, 각 전이는 확률 1(결정적)로 설정된다. 모델 체커 PRISM에 의해 PCTL 식 P =?

댓글 및 학술 토론

Loading comments...

의견 남기기