TSX 기반 사이드채널로 UMIP와 디스크립터 테이블 탈출 우회

초록

본 논문은 Intel TSX(Transaction Synchronization Extensions)를 이용한 타이밍 사이드채널 공격으로 커널의 GDT·IDT 주소를 유출하고, 이를 통해 UMIP와 하이퍼바이저 기반 디스크립터‑테이블 차단을 우회하는 방법을 제시한다. 최신 Meltdown·Spectre 패치와 Windows VBS·Hyper‑V 환경에서도 동작함을 실험으로 입증하고, 소프트웨어 기반 완화책을 제안한다.

상세 분석

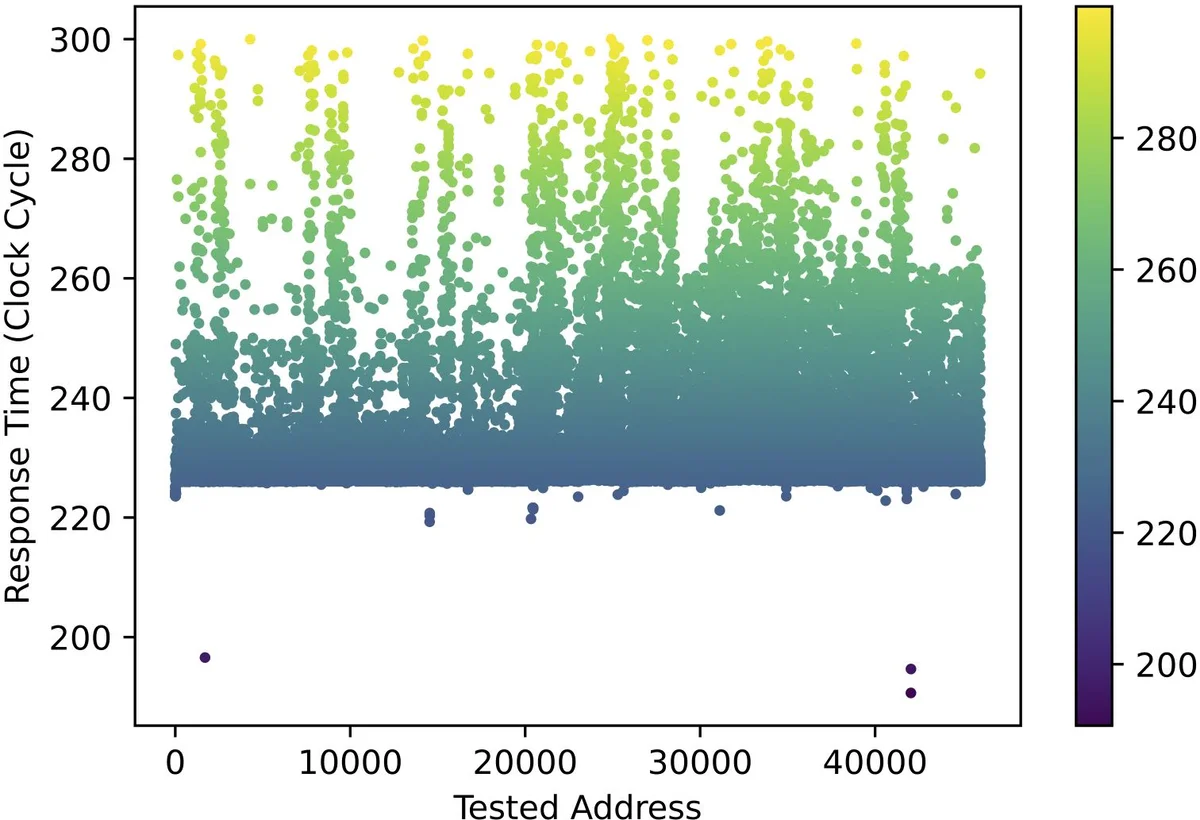

이 연구는 현대 운영체제에서 커널 주소 공간을 보호하기 위해 도입된 KASLR·KAISER·KPTI와 같은 메모리 격리 메커니즘을 전제로 한다. 그러나 GDT(Global Descriptor Table)와 IDT(Interrupt Descriptor Table)는 프로세서가 특권 전환을 위해 반드시 접근해야 하는 구조체이며, 그 물리·가상 주소가 완전히 숨겨지지는 않는다. 논문은 TSX의 트랜잭션 롤백 시 발생하는 미세한 캐시 타이밍 변화를 측정해, 특정 가상 주소에 대한 접근 성공 여부를 판단한다. 구체적으로, 공격자는 사용자 모드에서 SGDT·SIDT 명령을 실행하려 할 때, UMIP가 활성화돼 있으면 #GP 예외가 발생한다. 하지만 TSX 트랜잭션 내부에서 이러한 명령을 시도하면 예외가 트랜잭션 롤백으로 처리되어 프로세스가 중단되지 않는다. 롤백 전후의 캐시 상태 차이를 측정함으로써, 공격자는 “주소가 매핑돼 있다/없다”를 판단하고, 이진 탐색 형태로 GDT·IDT의 정확한 커널 가상 주소를 복원한다.

주소를 확보한 뒤에는 두 가지 주요 악용 경로가 제시된다. 첫째, 발견된 GDT 주소를 이용해 LGDT 명령으로 사용자 정의 세그먼트를 삽입하고, call‑gate를 설정해 사용자 모드에서 링0 코드 실행을 가능하게 한다. 둘째, IDT 주소를 알아내면 악성 인터럽트 핸들러를 삽입해 커널 권한 상승이나 시스템 전체 장악을 수행할 수 있다. 특히, 논문은 Windows 10/11, 최신 Linux 커널, macOS Monterey 이상에서 9세대 Intel 코어 프로세서를 대상으로 실험했으며, Hyper‑V와 VBS가 활성화된 가상화 환경에서도 동일한 절차가 성공함을 보여준다.

보호 메커니즘인 Descriptor‑Table Exiting(보조 프로세서 기반 VM‑Execution Control)도 검토했는데, 이 비트가 설정돼 있으면 LGDT·SIDT 등 명령이 VM‑Exit을 일으키게 된다. 그러나 공격자는 TSX 트랜잭션 내부에서 이러한 명령을 실행하면 VM‑Exit이 발생하지 않으며, 따라서 하이퍼바이저 차원의 방어를 회피한다.

마지막으로 논문은 완화 방안으로 (1) SGDT·SIDT 등 디스크립터‑테이블 접근을 제한하는 VM‑Execution Control 비트를 기본값으로 활성화하고, (2) 커널에서 GDT·IDT를 사용자 페이지에 매핑하지 않도록 페이지 테이블을 재구성하며, (3) TSX 사용을 제한하거나 트랜잭션 롤백 시 캐시 상태를 무작위화하는 소프트웨어 패치를 제안한다. 제안된 완화책은 실험에서 평균 3~5%의 성능 오버헤드만을 발생시켜 실용성이 높다.

댓글 및 학술 토론

Loading comments...

의견 남기기